# Proceedings

October 18 – 19, 2018 Sheraton Hsinchu Hotel Zhubei City, Taiwan

THE.

### Welcome to SWTest Asia 2018 1<sup>st</sup> Annual SWTest Asia Conference

#### Welcome SWTest Asia Attendee!

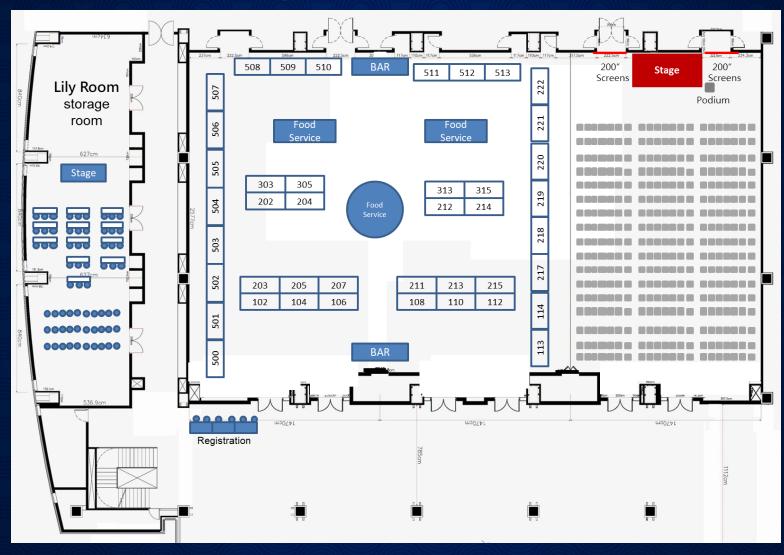

On behalf of the SWTest Asia Team it is our great pleasure to welcome you to the inaugural SWTest Asia Conference and EXPO at the Sheraton in Hsinchu, Taiwan. We would like to thank the sponsors (9-platinum, 2-gold, and 9-silver), the 42 exhibitors, and SWTest Team for their support to make SWTest Asia a valuable event for the Asian wafer test community.

For the 1<sup>st</sup> Annual Conference, we are pleased to have a Technical Program with 8 outstanding podium presentations and two excellent Keynotes from Dr. Harry Chen, Chair of the MediaTek Design Technology R&D Lab, and from Lin Fu, Ph.D., and John West of VLSI Research.

During the 2018 SWTest Asia EXPO, premier suppliers to the wafer test industry will have an opportunity to showcase their latest product offerings and technical services. New for SWTest Asia, we have created a "Tech Showcase" Track for Platinum Sponsors during which they will make short presentations and/or have product demonstrations.

Once again, thank you for being a part of the 1<sup>st</sup> Annual SWTest Asia Conference and EXPO; and we hope that you enjoy your time in Taiwan and the Hsinchu area.

Jerry Broz, Ph.D. General Chair, SWTest Asia International Test Solutions

Clark Liu Program Chair, SWTest Asia Powertech Technology, Inc.

**Rey Rincon** Program Co-Chair, SWTest Asia Translarity, Inc.

Maddie Harwood Finance Chair & Conference Management, SWTest Asia

**2018** SWTest Asia Conference

PROGRAM SCHEDULE

### SWTest Asia 2018 Platinum Sponsors

**2018** SWTest Asia Conference

PROGRAM SCHEDULE

### SWTest Asia 2018 Gold Sponsors

### SWTest Asia 2018 Silver Sponsors

Hitachi Chemical Working On Wonders

Technical Innovation - Physical Solutions

#### "Program Overview At A Glance"

| Day One       | Thursday, October 18th, 2018                                                                                       |

|---------------|--------------------------------------------------------------------------------------------------------------------|

| 9:00 - 12:00  | Exhibitor Registration Open<br>Exhibitor Setup in Expo Hall with 42 booths – Exhibitors Only                       |

| 12:00         | Attendee Registration Open                                                                                         |

| 12:00 - 16:00 | Attendee Registration Open<br>Expo Open                                                                            |

| 12:00 - 14:00 | Lunch in Expo Hall – Two Sessions                                                                                  |

| 15:00 – 16:00 | Tea Break in Expo Hall                                                                                             |

| 16:00 – 17:00 | Chair's Opening Remarks<br>Thursday Keynote Presentation in Chapel Room<br>Dr. Lin Fu and John West, VLSI Research |

| 17:00 - 18:00 | Welcome Reception in Expo Hall                                                                                     |

| Day Two       | Friday, October 19th, 2018                                                                                                                        |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8:00 – 17:00  | Attendee Registration Open                                                                                                                        |  |

| 8:30 – 9:15   | Chair's Opening Remarks<br>Friday Keynote Presentation in General Session Room<br>Dr. Harry Chen<br>Chair of MediaTek's Design Technology R&D Lab |  |

| 9:15 – 10:00  | Expo Open & Tea Break in Expo Hall                                                                                                                |  |

| 10:00 - 12:00 | "Innovations for the Next Generation of Test" in General Session Room<br>Full Conference Only<br>Expo Open                                        |  |

| 12:00 - 14:00 | Expo Open – Lunch in Expo Hall – Two Sessions                                                                                                     |  |

| 14:00 - 16:00 | <b>"Asia Probing Spotlight" in General Session Room</b><br>Full Conference Only<br>Expo Open                                                      |  |

| 16:00 – 16:15 | Awards for Best Presentations                                                                                                                     |  |

| 16:15 – 17:00 | Closing Reception in Expo Hall                                                                                                                    |  |

There will be a total of eight 30-minute technical papers, 14 hours of Expo, 2 tea breaks, 2 lunches, and 2 receptions

### PROGRAM SCHEDULE

#### **Program Overview**

After 28 years in San Diego, California, the SWTest Team is proud to announce our 1st Annual SWTest Asia conference to be held in Hsinchu, Taiwan, October 18-19, 2018. This one and one-half day conference will be a probe technology forum where attendees come to learn about recent developments in the industry and exchange ideas. As with SWTest in San Diego, CA, there will be a very relaxed atmosphere with Technical Sessions, an EXPO, and a Tech Showcase, as well as our signature relaxed environment for "informal discussion and networking".

This inaugural event has attracted attendees from the local and regional semiconductor industry to include ASE, TSMC, Ardentec, KYEC, SPIL, Micron, ChipMOS, UMC, Winbond, PTI, and more. Visitors to the conference will come from Japan, Korea, China, Singapore, India, Philippines, and Malaysia. Conference registration includes all meals, refreshments, social activities, and technical program and exhibit attendance, as well as the eProceedings.

| Thursday, October 18th, 2018             |                                                                                                                                                                                            |                          |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 9:00 – 12:00                             | Exhibitor Registration Open<br>Exhibitor Setup in Expo Hall with 42 booth                                                                                                                  | s – Exhibitors Only      |

| 12:00 - 16:00                            | Attendee Registration Open<br>Expo Open                                                                                                                                                    |                          |

| 12:00 - 14:00                            | Lunch in Expo Hall – Two Sessions                                                                                                                                                          |                          |

| 15:00 - 16:00                            | Tea Break in Expo Hall                                                                                                                                                                     |                          |

| 16:00 – 17:00<br>Space Available Seating | Dr. Jerry Broz, SWTest General Chair<br>Clark Liu, SWTest Technical Program Chair<br>Thursday Invited Presentation in Chapel R<br>Semiconductor Industry Er<br>World Finds Ways to Extract | ntering a New Era as the |

| 17:00 – 18:00                            | Welcome Reception in Expo Hall                                                                                                                                                             |                          |

#### PROGRAM SCHEDULE

| Program Overview<br>Friday, October 19th, 2018 |                                                                                                                                                                                                                                                                                                                    |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                |                                                                                                                                                                                                                                                                                                                    |  |

| 8:30 – 9:30                                    | Welcome to SWTest Asia 2018Dr. Jerry Broz, SWTest General ChairClark Liu, SWTest Technical Program ChairFriday Keynote Presentation in General Session RoomFacing Test Challenges in Upcoming Al/5G-<br>based Systems Opportunity for Radical IdeasDr. Harry Chen<br>Chair of MediaTek's Design Technology R&D Lab |  |

| 10:00 - 12:00                                  | <i>"Innovations for the Next Generation of Test"</i> in General Session Room<br>Full Conference Only<br>Expo Open                                                                                                                                                                                                  |  |

| 12:00 - 14:00                                  | Expo Open – Lunch in Expo Hall – Two Sessions                                                                                                                                                                                                                                                                      |  |

| 14:00 - 16:00                                  | <b>"Asia Probing Spotlight" in General Session Room</b><br>Full Conference Only<br>Expo Open                                                                                                                                                                                                                       |  |

| 16:00 - 17:00                                  | Expo Open<br>Closing Reception in Expo Hall                                                                                                                                                                                                                                                                        |  |

2018

SWTest Asia Conference

### PROGRAM SCHEDULE

| Program Overview    |                                                                                                                                                                                                                                                                                                                                                          |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Technical Session 1 | Innovations for the Next Generation of Test<br>Session Chair: <u>Dr. Jerry Broz,</u> General Chair (International Test Solutions)                                                                                                                                                                                                                        |  |

| 10:00 - 10:30       | Next Generation OSAT – Innovative Circuit Probing with AI implement<br>Huang Po-Hao (TeraPower Technology Inc. – Taiwan)                                                                                                                                                                                                                                 |  |

| 10:30 - 11:00       | Wafer Level Efficient Characterization and Testing of MRAM<br><u>Dr. Siamak Salimy</u> (Hprobe – France)<br>Hantsun Chung (Hermes Epitek - Taiwan)                                                                                                                                                                                                       |  |

| 11:00 - 11:30       | Overcoming Challenges for 5G Production Tests<br>Dr. Choon Beng Sia (FormFactor, Inc. – Singapore)                                                                                                                                                                                                                                                       |  |

| 11:30 – 12:00       | Simulation and verification of FeinProbe Probe Card Model for the 5G WLCSP<br>Application<br><u>Krzysztof Dabrowiecki</u> (Feinmetall GmbH – Germany)<br><u>Adrian Lim</u> (Feinmetall GmbH – Singapore)<br>Jose Moreira (Advantest – Germany)<br>Thomas Gneiting and Ali Abdallah (AdMOS – Germany)<br>Paul Hurst (Harbor-Electronics – United Kingdom) |  |

| 12:00 - 14:00       | Expo Open – Lunch in Expo Hall – Two Sessions                                                                                                                                                                                                                                                                                                            |  |

| Technical Session 2 | <b>Technical Session 2 – Asia Probing Spotlight</b><br><b>Session Chair:</b> <u>Clark Liu</u> , Program Chair (Powertech Technology, Inc.)                                                                                                                     |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

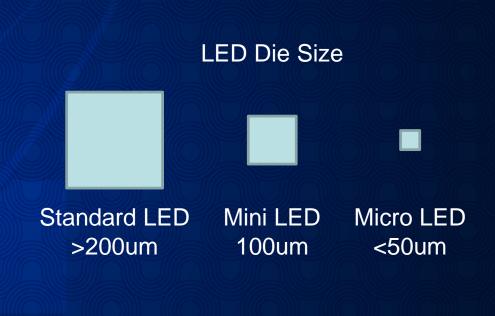

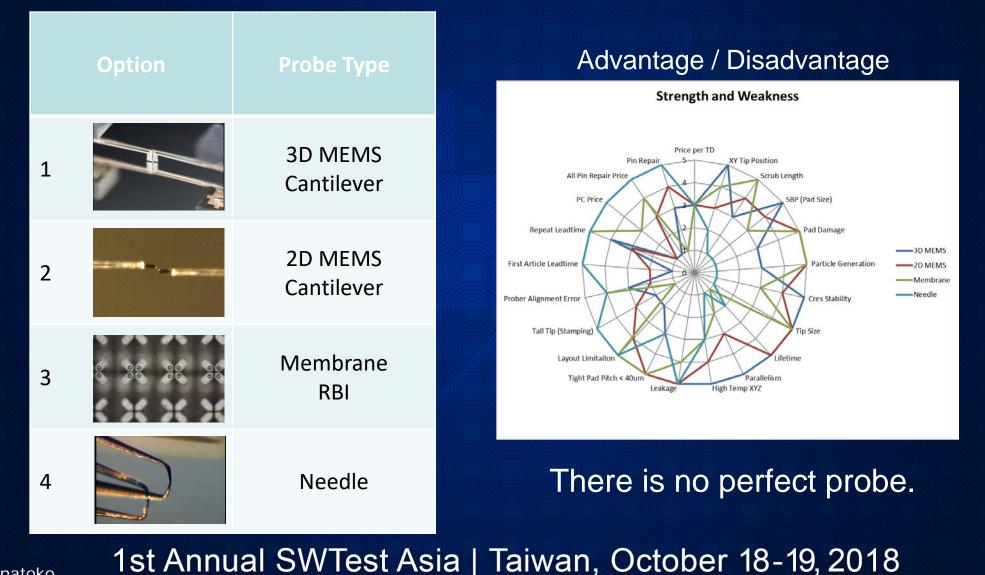

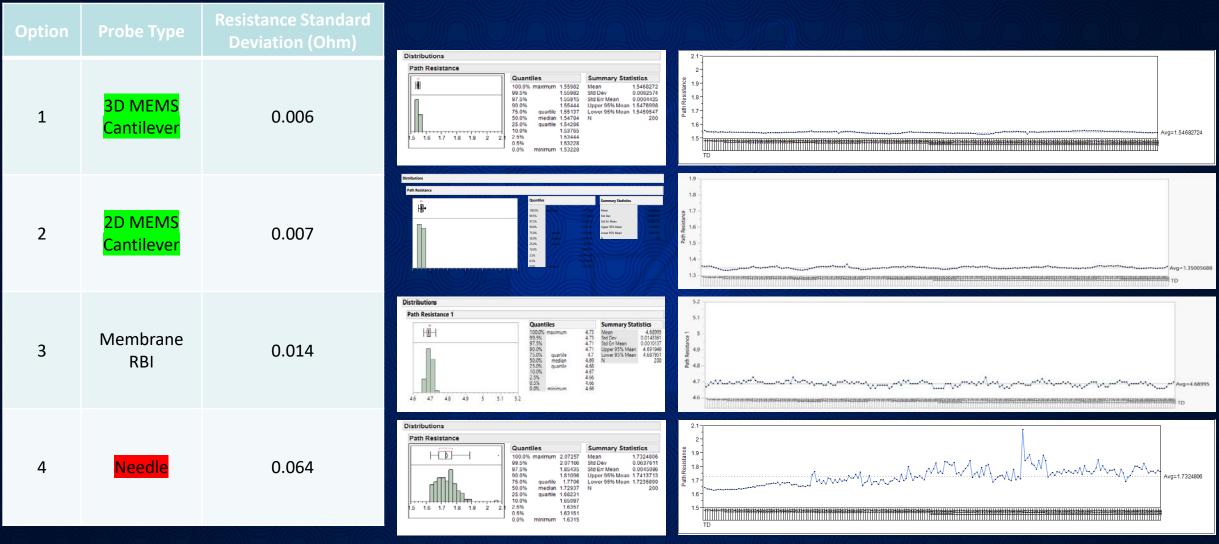

| 14:00 - 14:30       | LED Wafer Probe Test<br>Yoichi Funatoko (FormFactor, Inc. – Japan)                                                                                                                                                                                             |

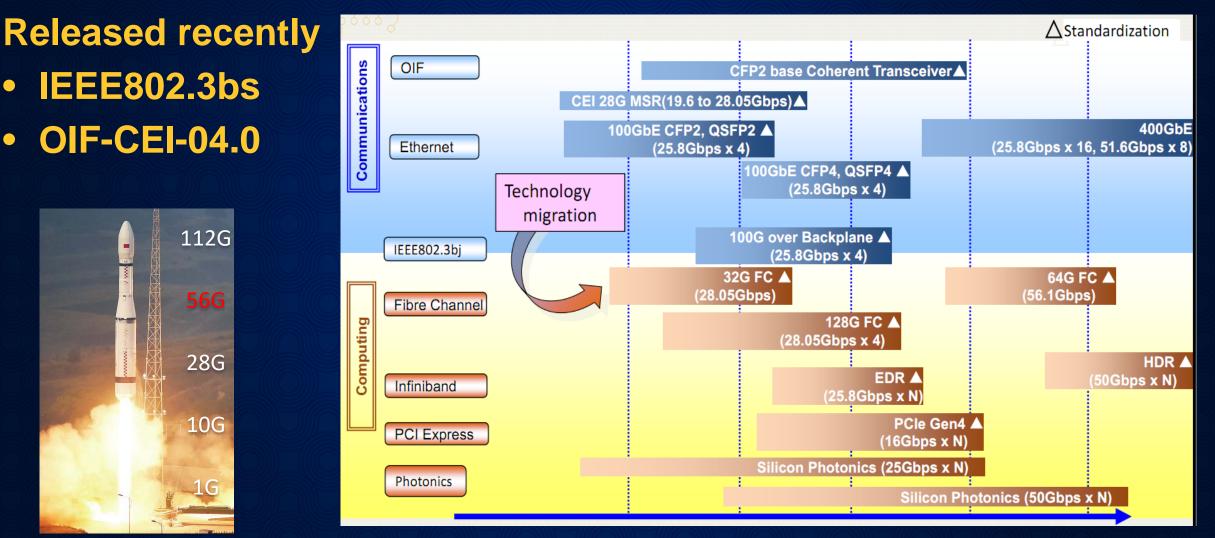

| 14:30 – 15:00       | Improve the Accuracy of High Speed Simulation to Meet 56G/112G Testing<br>Requirement on PCB<br>Jackie Luo (Shanghai Zenfocus Semi-Tech Co.,Ltd – China)                                                                                                       |

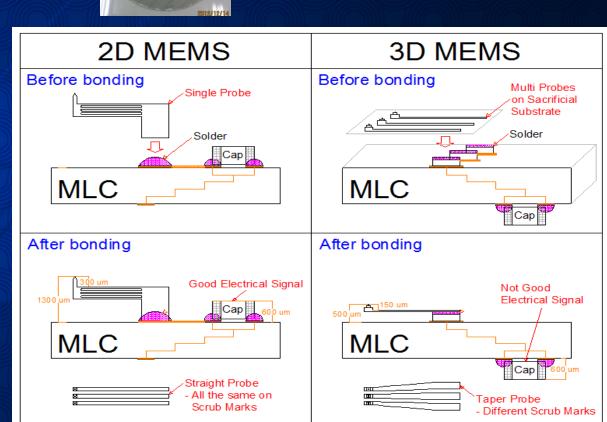

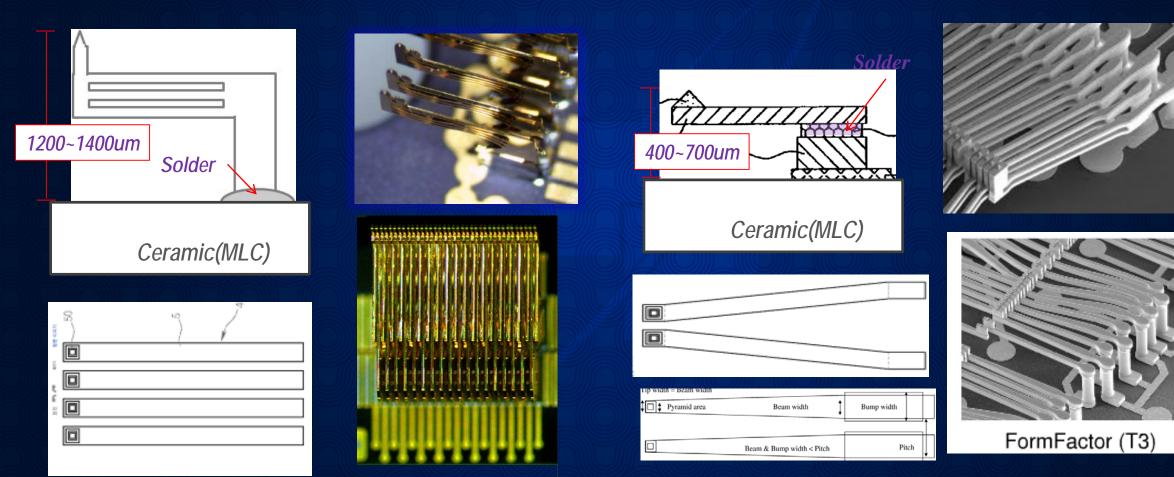

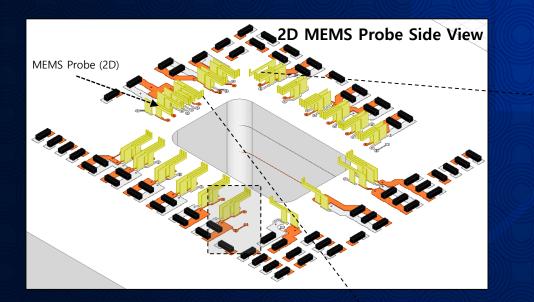

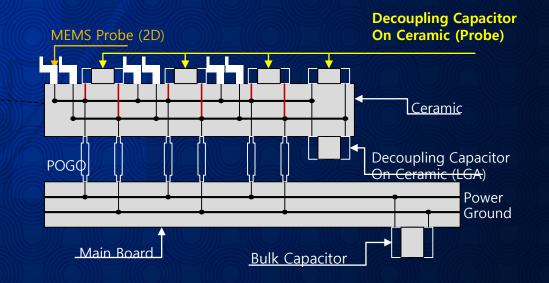

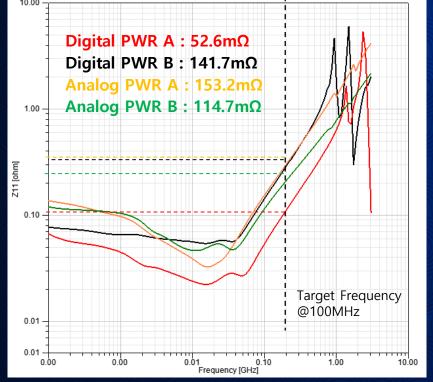

| 15:00 – 15:30       | High Performance CIS Wafer Probing using 2D MEMS TechnologyDr. Yunhwi Park, Kyungsub Kim, Youngjin Kim, and Sungjoon Kang (KoreaInstruments – Korea)Chang-Hoon Hyun (Samsung Electronics/S.LSI Division – Korea)Kyushik Min (Samsung Electronics. Co. – Korea) |

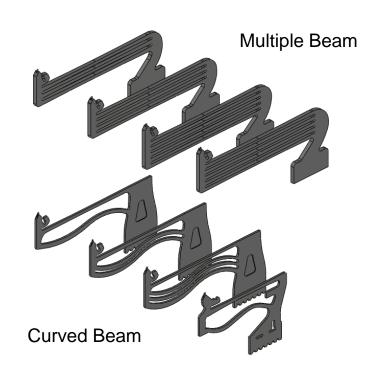

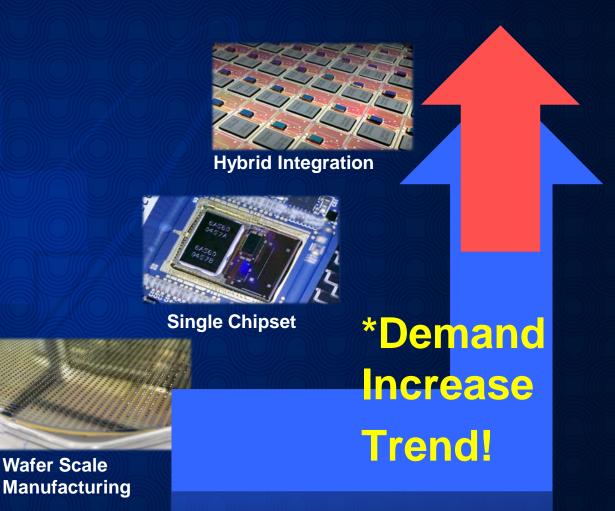

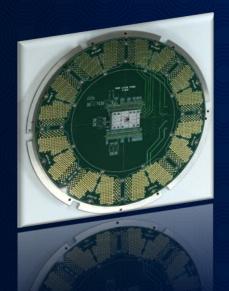

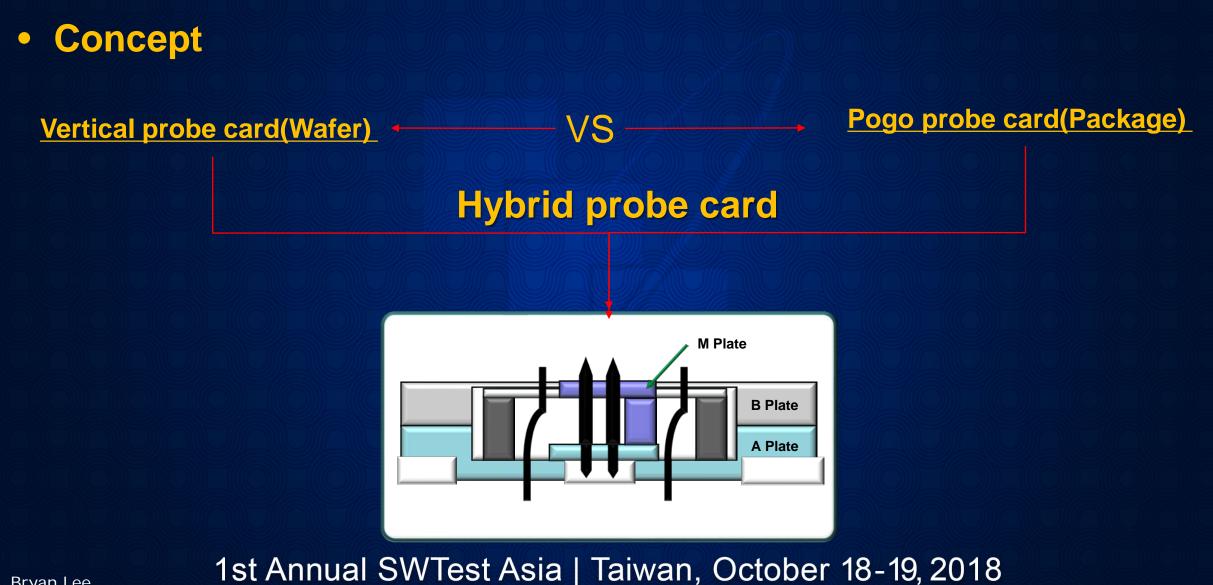

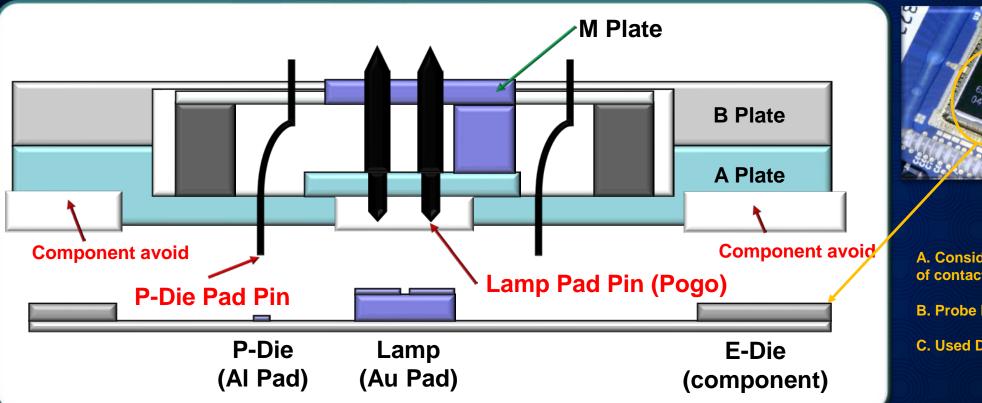

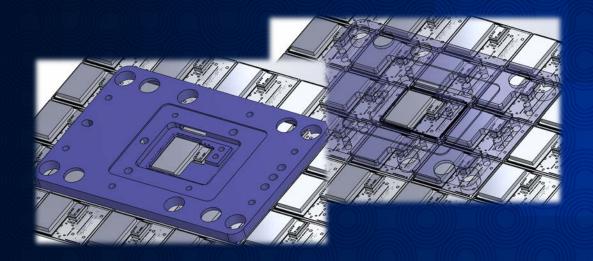

| 15:30 - 16:00       | Hybrid Type (Mixed Probe Types) Vertical Probe Card<br>Bryan Lee and James Park (TEPS Co., Ltd – Korea)                                                                                                                                                        |

| 16:00 - 16:15       | Awards for Best Presentations                                                                                                                                                                                                                                  |

| 16:15 – 17:00       | Closing Reception in Expo Hall                                                                                                                                                                                                                                 |

#### PROGRAM SCHEDULE

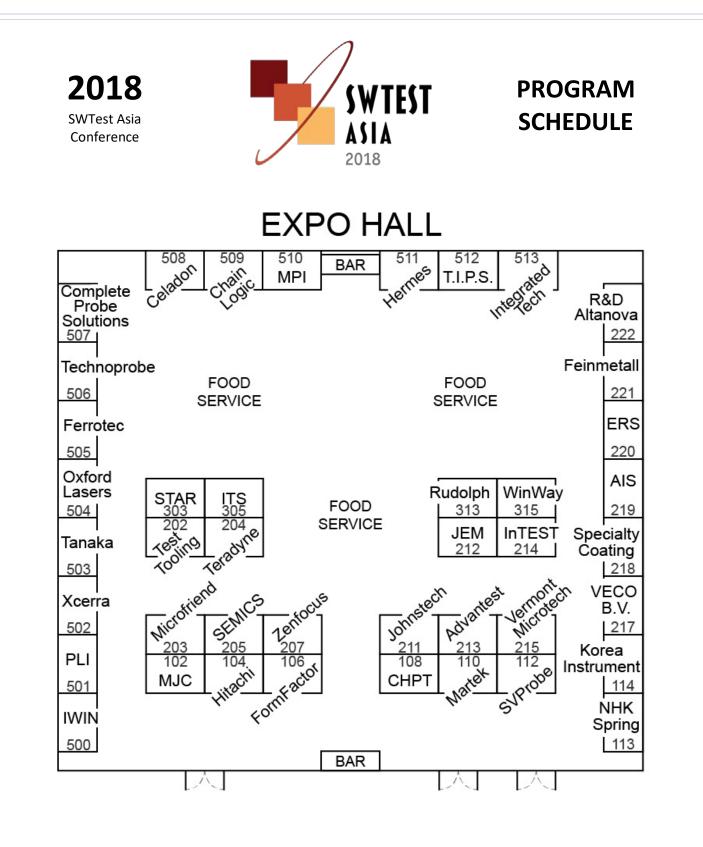

### **2018 EXHIBITORS**

**Advantest Corporation** AIS Technology, Inc. **Celadon Systems** Chain-Logic International Corp. CHPT **Complete Probe Solutions ERS electronic GmbH** Feinmetall GmbH **Ferrotec Ceramics Corporation** FormFactor Hermes Testing Solutions Inc. Hitachi Chemical Co., Ltd. Integrated Technology Corporation International Test Solutions InTEST Corporation IWIN Co., Ltd. JEM Taiwan Johnstech International Korea Instrument MarTek, Inc Microfriend Inc.

MJC Taiwan **MPI** Corporation NHK Spring Co., Ltd. Nidec SV TCL **Oxford** Lasers PLI Co.,Ltd **R&D** Altanova Rudolph Technologies, Inc. SEMICS Shanghai Zenfocus Semi-Tech Co., Ltd Specialty Coating Systems STAr Technologies, Inc. T.I.P.S. Messtechnik GmbH **Tanaka Precious Metals** Technoprobe America Inc. Teradyne, Incorporated **Test Tooling Solutions Group** Veco B.V. Vermont Microtechnologies WinWay Technology **Xcerra Corporation**

PROGRAM SCHEDULE

# 2<sup>nd</sup> Annual SWTest Asia

# Coming in October, 2019 (dates will be announced soon!)

2018 SWTest Asia Conference

PROGRAM SCHEDULE

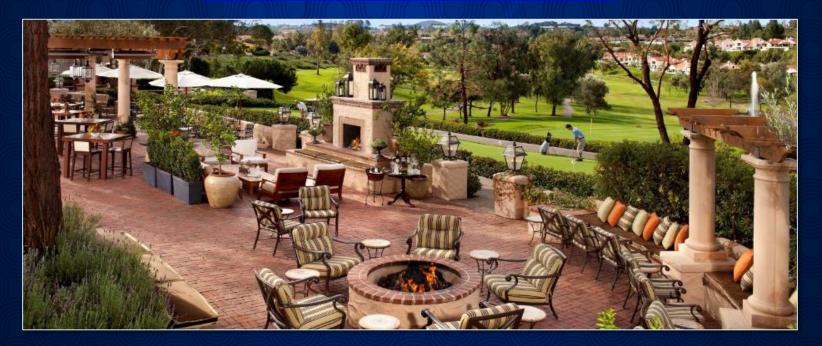

### Save The Dates SWTest Workshop 2019

Rancho Bernardo Inn, San Diego, CA June 2 - 5, 2019

Abstract Submission Date March 5, 2019

> Golf Tournament June 2, 2019

# See You Next Year!

# **Thanks for your Support !**

## Contact the SWTest Asia Team with any questions

Jerry Broz, Ph.D. General Chair SWTest Asia +1-303-885-1744 E: jerry.broz@swtest.org Clark Liu Asia Technical Program Chair SWTest Asia +886-975-658-563 E: clark.liu@swtest.org

Rey Rincon Technical Program Co-Chair SWTest Asia +1-214-402-6248 E: rey.rincon@swtest.org Maddie Harwood Finance Chair & Conference Management SWTest Asia +1-540-937-5066 E: maddie.harwood@swtest.org E: expo@swtest.org

# **TERMS of SERVICE**

- Information included in the SWTest proceedings and websites reflect the authors opinions and are presented without change. Inclusion in any workshop proceedings (past or present) does not constitute an endorsement by the SWTest, SWTest Asia, IEEE Society, CPMT Society, Computer Society, and/or the Test Technology Council.

- SWTest and SWTest Asia publications and websites contain information that has been provided by exhibitors, sponsors, and authors. Exhibitors, sponsors, and authors are responsible for ensuring that materials submitted for inclusion within the SWTest and SWTest Asia publications and associated sites are accurate as well as in compliance with any applicable laws. SWTest and SWTest Asia does not investigate, edit without permission, or check the accuracy of the submitted materials.

- Papers previously copyrighted or with copyright restrictions cannot be presented. In keeping with a workshop environment and to avoid copyright issues, SWTest and SWTest Asia does not officially seek a copyright ownership or transfer from authors.

- Authors agree by submitting their work that it is original work and substantially not published previously or copyrighted, may be referenced in the work of others, will be assembled / distributed in the SWTest and SWTest Asia Proceedings, and made available for download by anyone from the SWTest and SWTest Asia website.

2<sup>nd</sup> Annual SWTest Asia Coming in October, 2019 (will be announced soon!)

# **Thanks for Attending SWTest Asia !**

# We Hope to See you at SWTest San Diego June 2 to 5, 2019 !!!

Rancho Bernardo Inn, San Diego, CA

# Technical Program SWTest Asia 2018

Friday, October 19, 2018

Taiwan, October 18-19, 2018

# Friday, October 19, 2018

### <u>08:30 to 09:30 – Welcome to SWTest Asia 2018</u>

### Welcome SWTest Asia 2018

Dr. Jerry Broz (SWTest Asia General Chair) and Clark Liu (SWTest Asia Program Chair)

### Facing Test Challenges in Upcoming AI/5G-based Systems Opportunity for Radical Ideas

**Dr. Harry Chen**

Chair of MediaTek's Design Technology R&D Lab

MEDIATEK

# Friday, October 19, 2018

### 10:00 to 12:00 – Innovations for the Next Generation of Test

Next Generation OSAT – Innovative Circuit Probing with AI implement Huang Po-Hao (TeraPower Technology Inc. – Taiwan)

Wafer Level Efficient Characterization and Testing of MRAM Dr. Siamak Salimy (Hprobe – France) and Hantsun Chung (Hermes Epitek – Taiwan)

> **Overcoming Challenges for 5G Production Tests** Dr. Choon Beng Sia (FormFactor, Inc. – Singapore)

Simulation and Verification of FeinProbe Probe Card Model for the 5G WLCSP Application <u>Krzysztof Dabrowiecki</u> and Adrian Lim (Feinmetall GmbH), Jose Moreira (Advantest), Thomas Gneiting and Ali Abdallah (AdMOS), and Paul Hurst (Harbor-Electronics – UK)

# Friday, October 19, 2018

14:00 to 16:30 – Asia Probing Spotlight

LED Wafer Probe Test Yoichi Funatoko (FormFactor, Inc. – Japan)

Improve the Accuracy of High Speed Simulation to Meet 56G/112G Testing Requirement on PCB Jackie Luo (Shanghai Zenfocus Semi-Tech Co., Ltd – China)

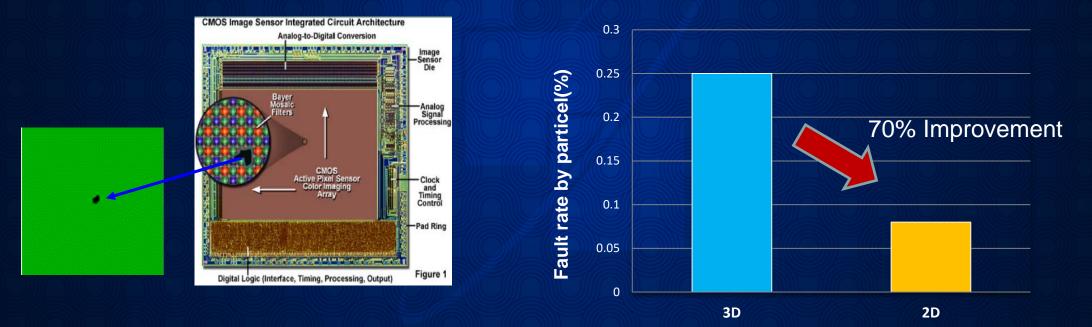

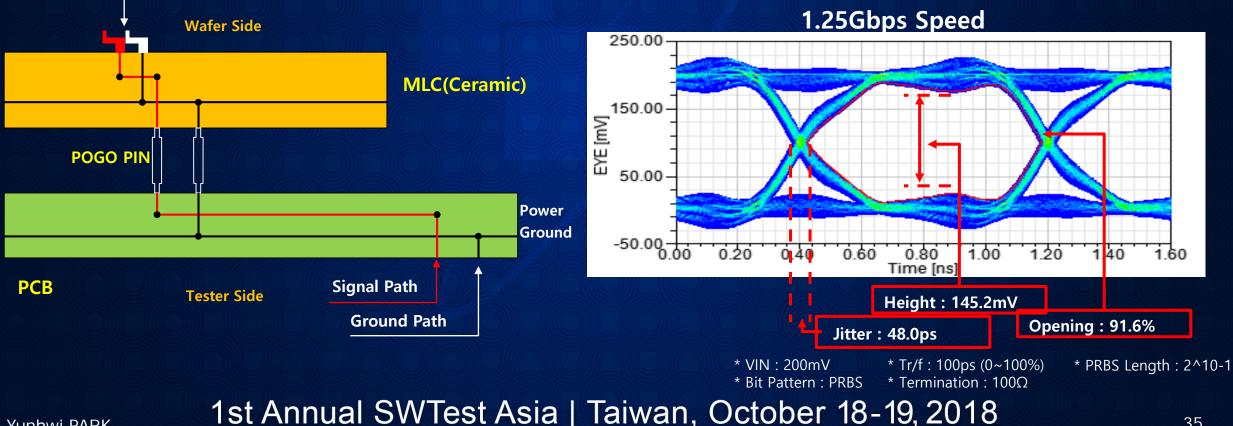

High Performance CIS Wafer Probing using 2D MEMS Technology

Dr. Yunhwi Park, Kyungsub Kim, Youngjin Kim, and Sungjoon Kang (Korea Instruments – Korea) Chang-Hoon Hyun and Kyushik Min (Samsung Electronics. Co. – Korea)

Hybrid Type (Mixed Probe Types) Vertical Probe Card

Bryan Lee and James Park (TEPS Co., Ltd – Korea)

# **Additional Presentations**

### **Please contact the authors regarding their work**

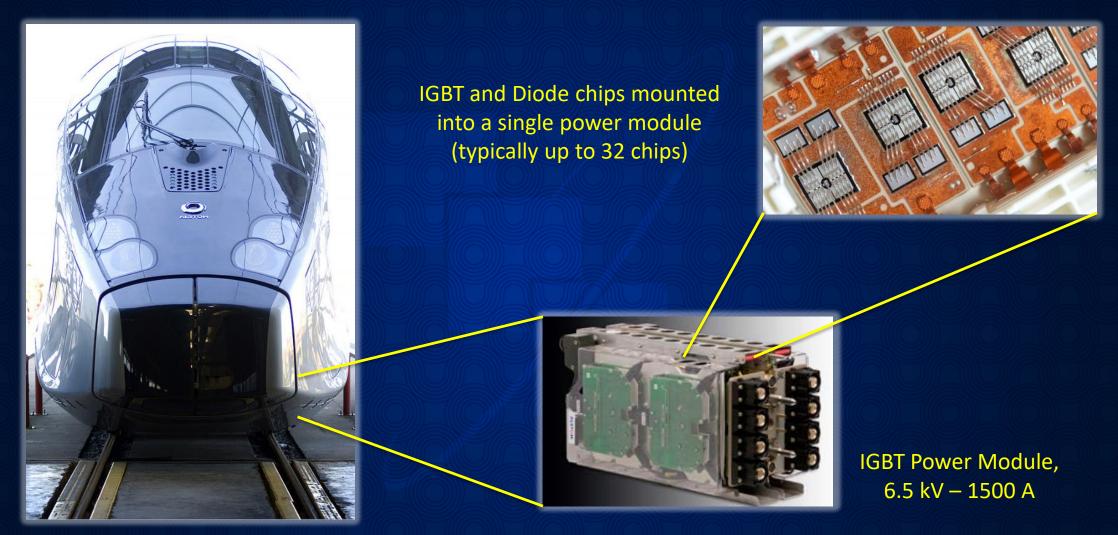

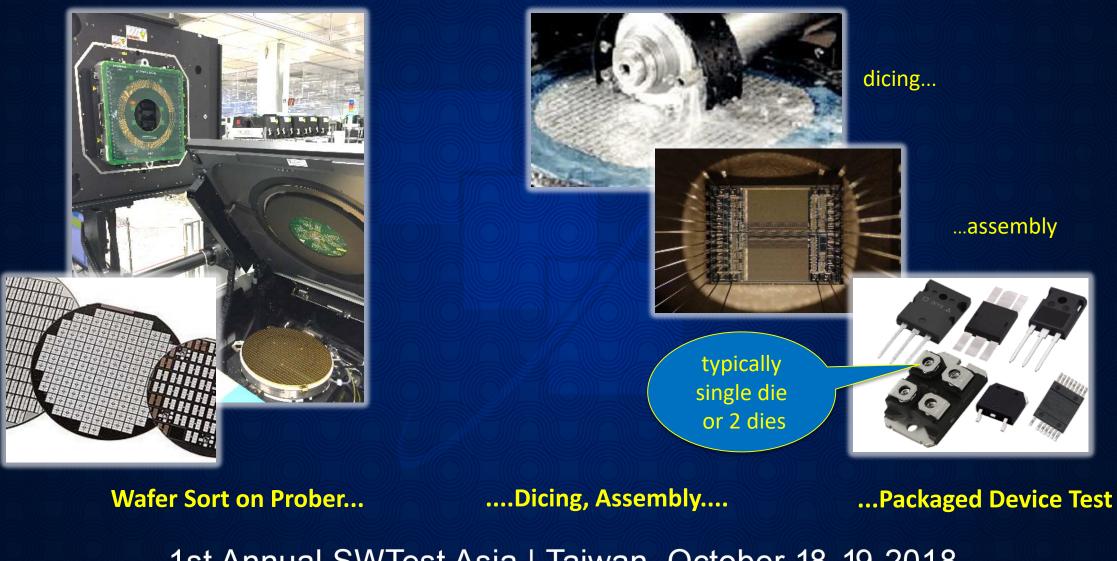

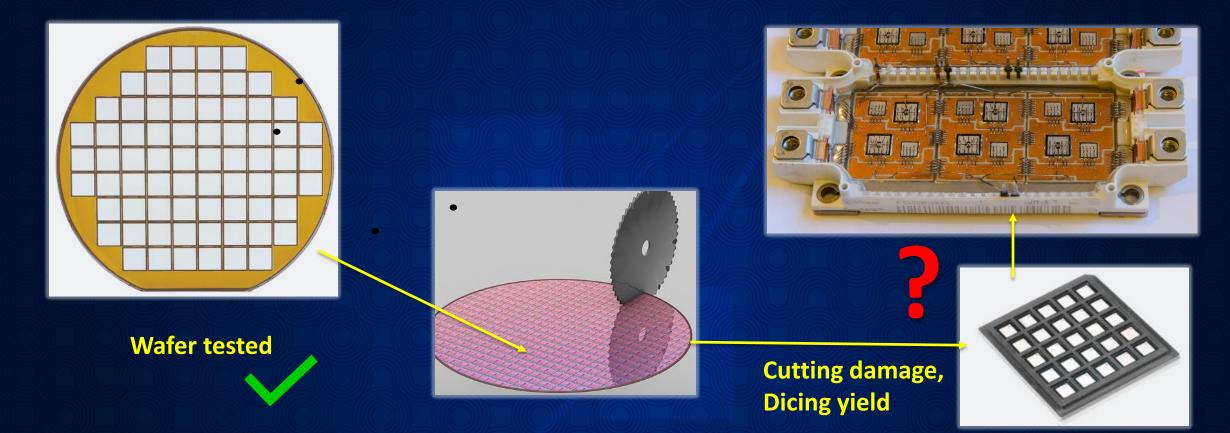

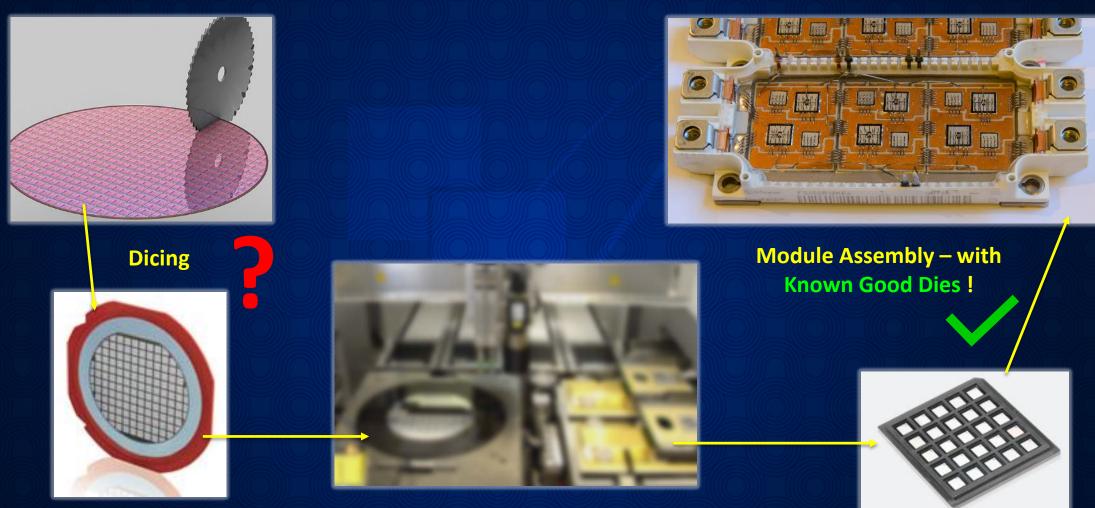

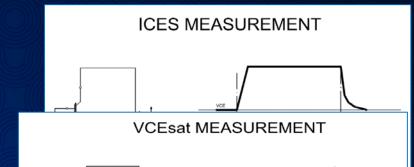

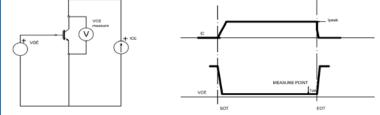

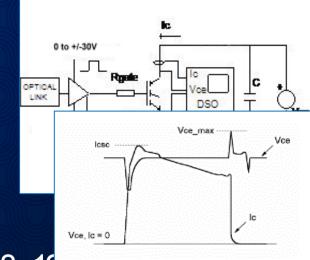

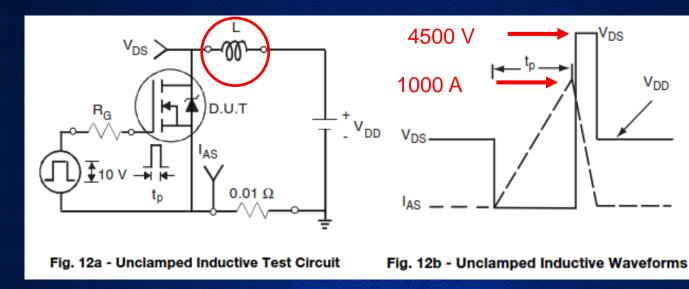

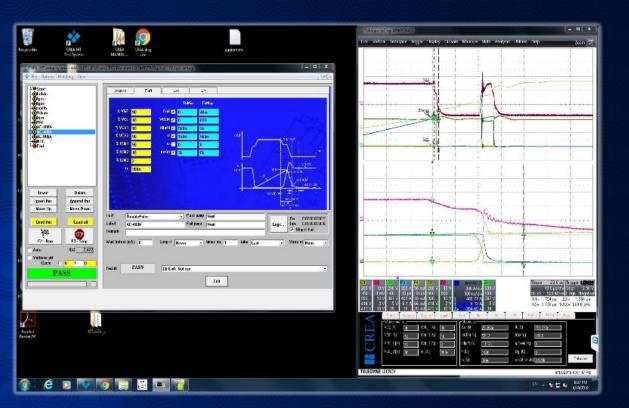

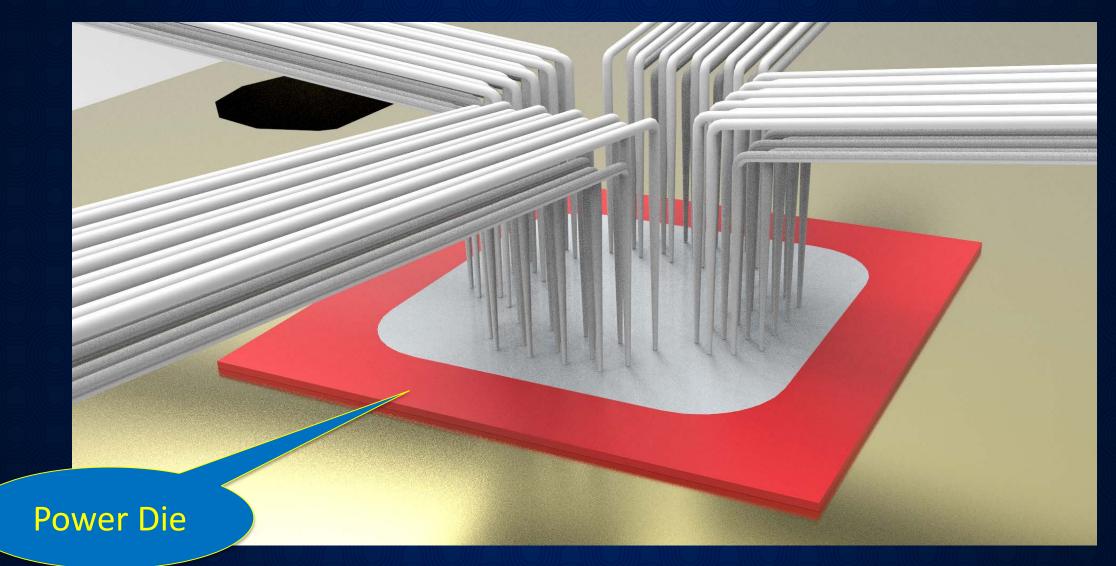

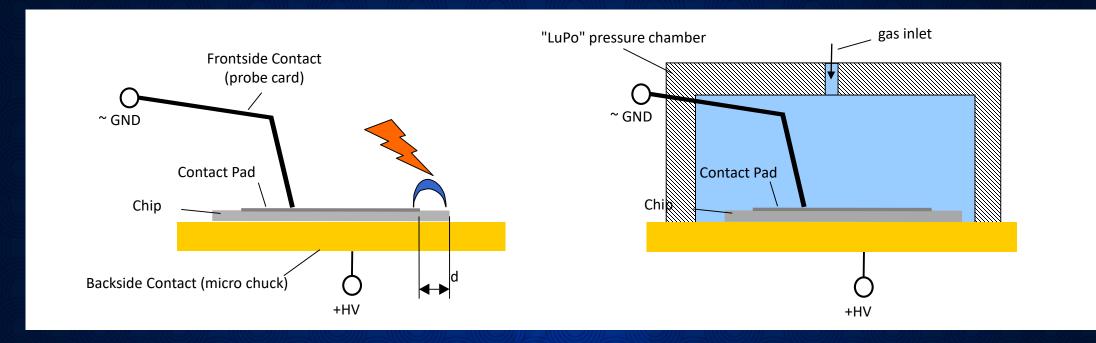

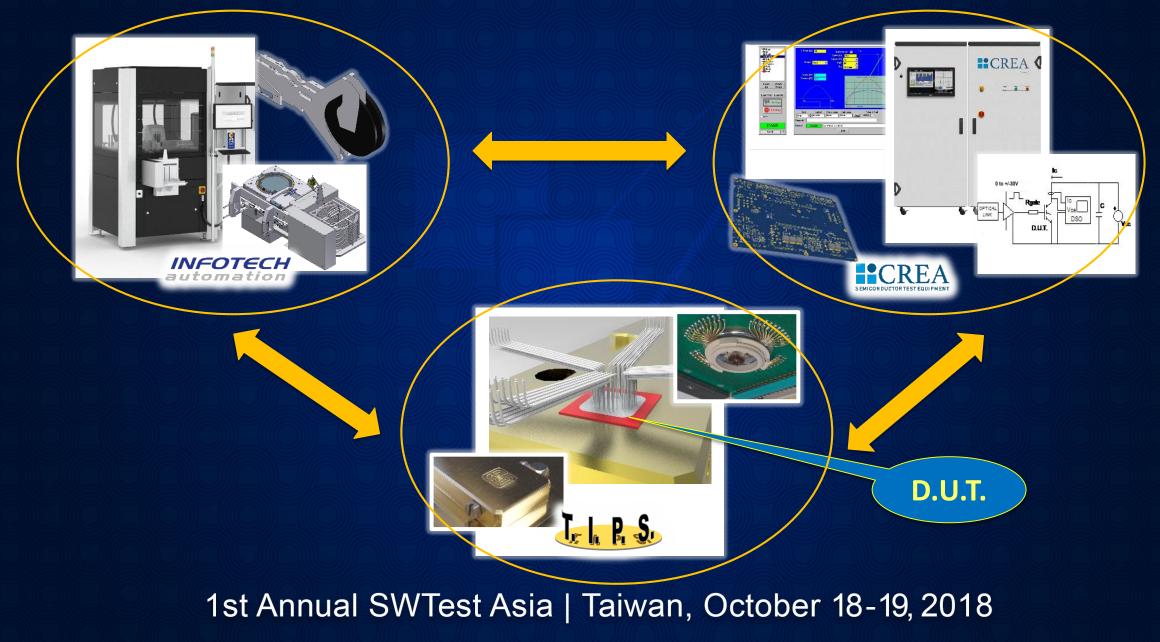

#### KGD – Known Good > POWER < Die Diced Wafer Test at 7 kV and 1000 A

Mauro Serra (CREA Test), Jens Lochbaum (INFOTECH Automatio) and Rainer Gaggl (T.I.P.S. Messtechnik)

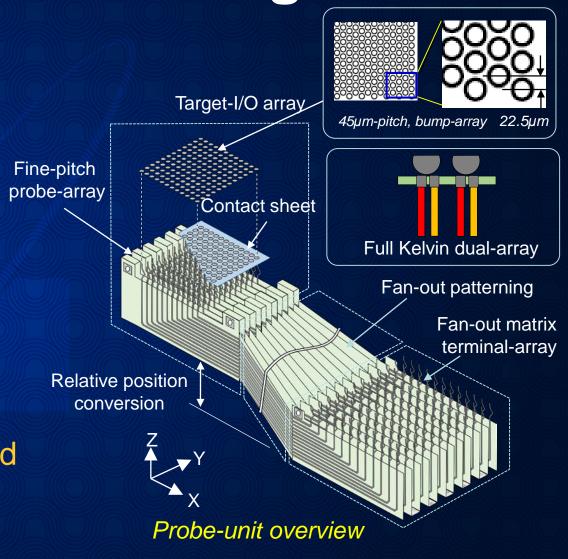

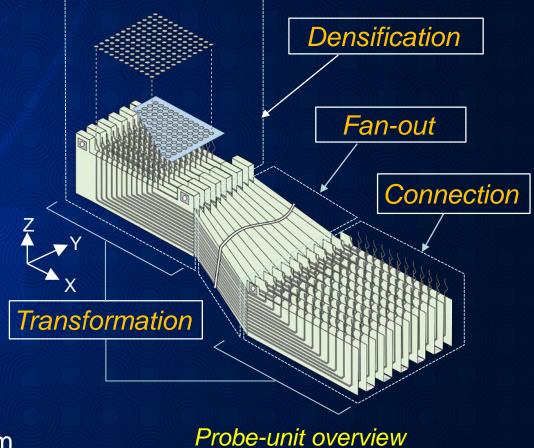

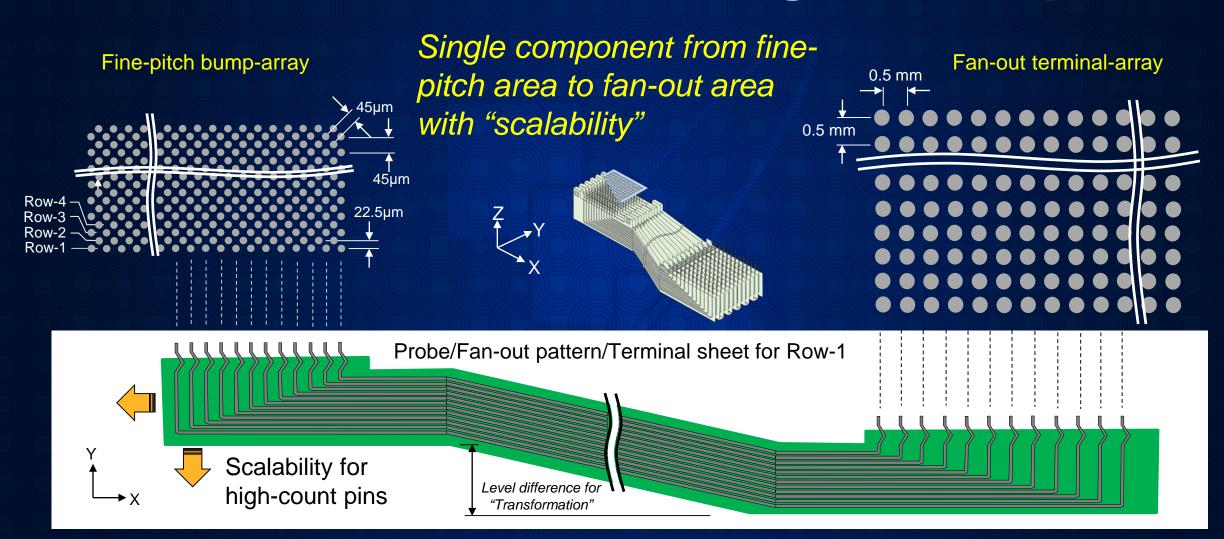

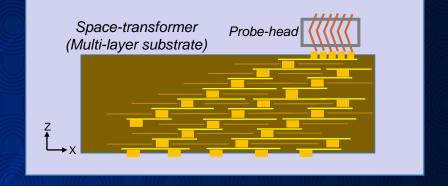

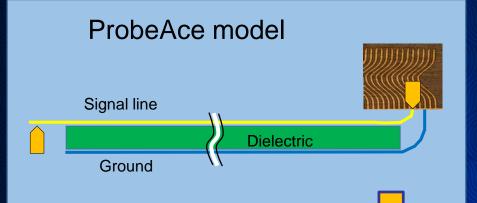

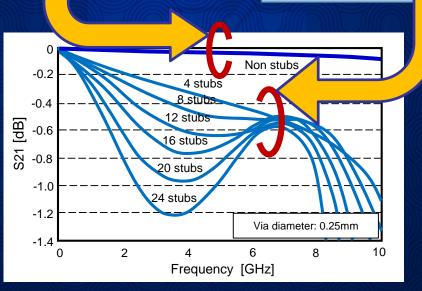

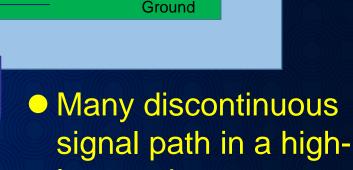

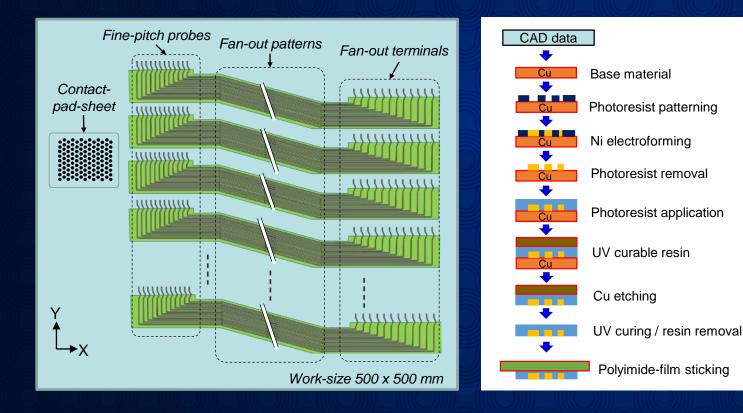

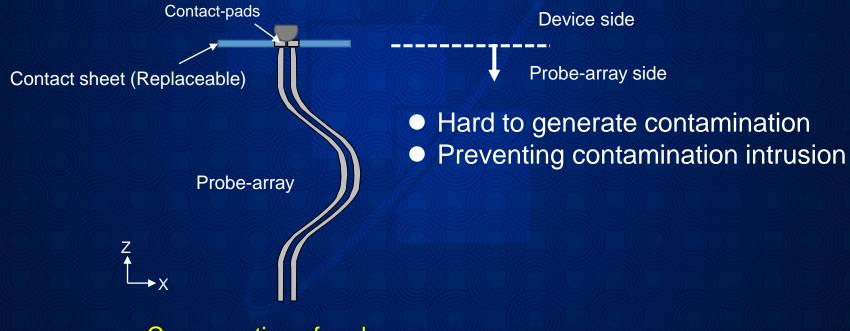

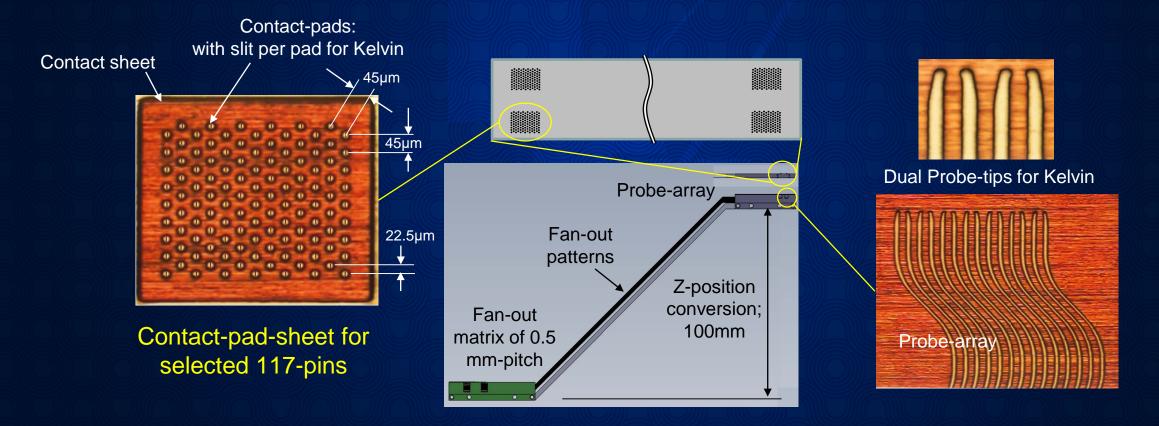

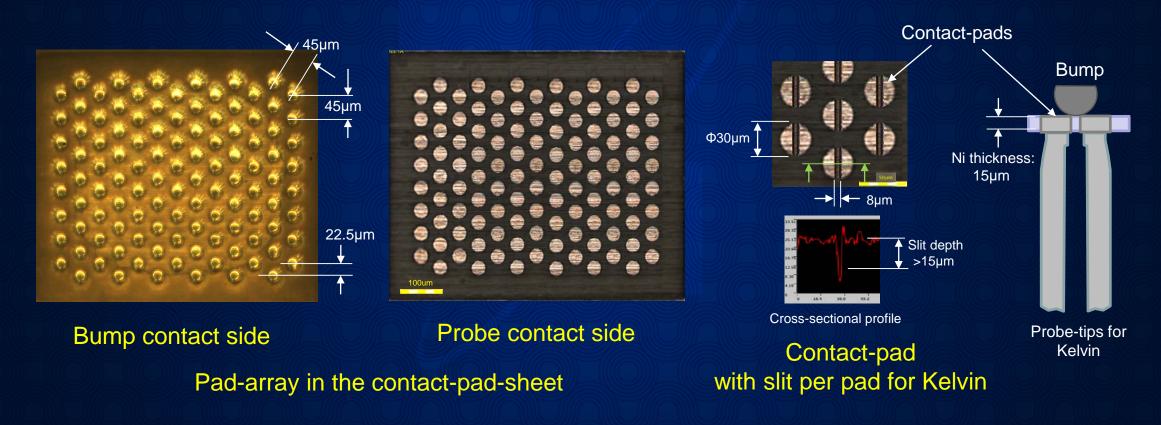

A High-density Area-array Probe-unit with Non-discontinuous Fan-out Structure without Space Transformer using Monolithic Fabrication Method Gunsei Kimoto, Takayuki Kakinuma, Masao Seimiya (ProbeAce Co.,Ltd. – Japan)

# Technical Program SWTest Asia 2018

Friday, October 19, 2018

Taiwan, October 18-19, 2018

# Welcome to the 1<sup>st</sup> Annual SWTest Asia in Taiwan

Jerry Broz, Ph.D. General Chair, SWTest Asia International Test Solutions Clark Liu Technical Program Chair, SWTest Asia Powertech Technology, Inc.

Taiwan, October 18-19, 2018

# Welcome to the Sheraton, Hsinchu !

# **SWTest San Diego and SWTest Asia**

- For 28 years, Semiconductor Wafer Test (SWTest) has been held annually in San Diego, CA, every June.

- SWTest is internationally recognized as the premier wafer test technology conference.

- Each year more than 500 industry leaders and technologists committed to solving problems and driving innovation attend.

- International attendance at SWTest has grown substantially; and, in 2018, almost 30% of the attendees came from Asia and Pacific Rim.

- SWTest Chairs decided to expand the conference because of Asia's tremendous technological importance to semiconductor and wafer level test.

- SWTest Team is proud to welcome you to the 1<sup>st</sup> Annual SWTest Asia Conference held in Hsinchu, Taiwan.

Held Annually During June In San Diego, CA

To be Held Annually During October In the Asia Region

# **SWTest Asia Chairs and Committee**

### • SWTest Asia Chairs

- Dr. Jerry Broz, General Chair (International Test Solutions)

- Clark Liu, SWTest Asia Technical Program Chair (Powertech Technology, Inc.)

- Rey Rincon, Technical Program Co-Chair (Translarity, Inc.)

- Maddie Harwood, Finance and Conference Management Chair

### SWTest Asia Committee Members

- Nobuhiro Kawamata, FormFactor K.K.

- Joey Wu, STAr Technologies

# Welcome to SWTest Asia 2018

#### SWTest Asia <u>IS</u> a Probe Technology Forum

- Technical Conference for Wafer Test Professionals

- Providing practical solutions to real problems faced by probing technologists

- Balanced mixture of presentations from semiconductor manufacturers, suppliers, and collaborations.

#### Informal Conference with a Relaxed Atmosphere

- "Workshop Style" conference focused on technical exchange

- Great opportunities for friendly discussions and networking

- Meet new people and have a little fun !

### • "Green Initiative" ...

eProceedings and enviro-friendly practices

# **Technical Program / Agenda**

### • Thursday, October 18

- SWTest Asia EXPO 2018 with 42-key suppliers

- SWTest Asia Technology Showcase Presentations with Platinum Sponsors

- Invited Presentation from <u>Dr. Lin Fu</u> and <u>John West</u> of VLSI Research

- Welcome Reception in Expo Hall

### • Friday, October 19

- Keynote from <u>Dr. Harry Chen</u>, Chair of MediaTek's Design Technology R&D Lab

- Technical Program with 2-podium sessions

- 1000 to 1200: Innovations for the Next Generation of Test

- 1400 to 1600: Asia Probing Spotlight

- SWTest Asia EXPO 2018 with 42-key suppliers

- SWTest Asia Technology Showcase Presentations with Platinum Sponsors

- Closing Reception in Expo Hall

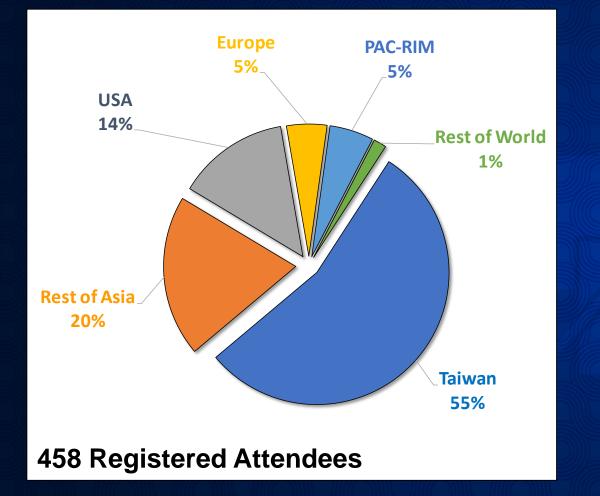

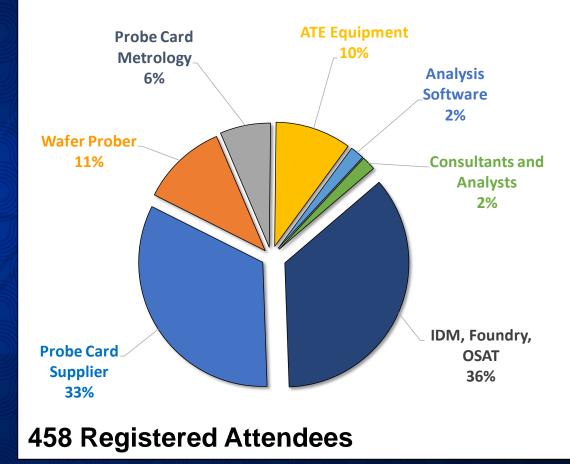

# **SWTest Asia 2018 Demographics**

# Map of the Area

# SWTest Asia 2018 eProceedings

eProceedings Password: <u>dragon</u>

- Conference e-Version is available for download in a password protected file.

- Go to ... http://www.swtestasia.org

- Ballroom WiFi Password =

- Free WiFi access will be available during the entire conference to allow attendee access to the downloads.

- Password for the download files will be announced throughout each day and at the registration desk.

- Non-password locked files (including the Keynote presentations) will be made available in the SWTest Asia Archives after the conference adjourns.

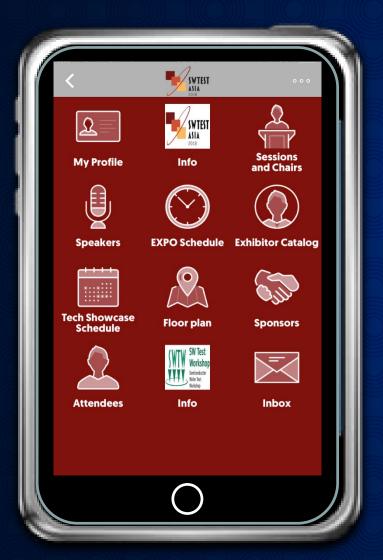

# SWTest Asia App – "In the Palm of Your Hand"

- Up-to-the-minute "Event Info"

- Schedules of the "Sessions"

- Connect with the "Speakers"

- Meet with the "Exhibitors" and "Sponsors"

- Attend the "Tech Showcase"

- Get oriented on the "Floorplan"

- Network with the "Attendees"

- Get important updates with "SWTest Inbox"

- Learn about "SWTest in San Diego"

# **Platinum Sponsors**

# **Gold Sponsors**

# **Silver Sponsors**

# **Thursday Invited Speakers**

"Semiconductor Industry Entering a New Era as the World Finds Ways to Extract More Value from Chips"

**VLSI**research

Dr. Lin Fu Technical and Market Analyst VLSI Research Europe John West Managing Director VLSI Research Europe

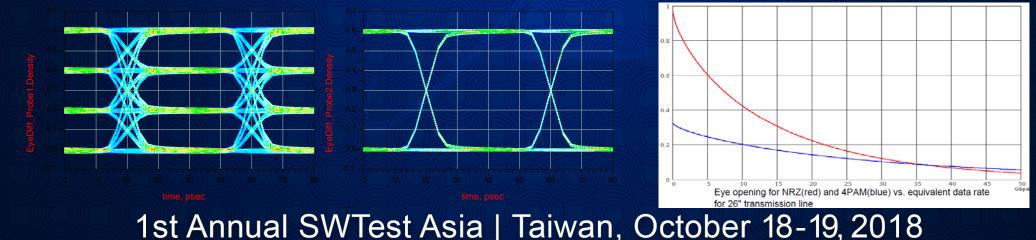

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

$\triangleright$

# Friday Keynote Speaker

Facing Test Challenges in Upcoming AI/5G-based Systems Opportunity for Radical Ideas

> Dr. Harry Chen Chair of MediaTek's Design Technology R&D Lab Mediatek, Inc.

> > ΜΕΟΙΛΤΕΚ

# Technical Program SWTest Asia 2018

Friday, October 19, 2018

Taiwan, October 18-19, 2018

### Friday, October 19, 2018

#### 10:00 to 12:00 – Innovations for the Next Generation of Test

Next Generation OSAT – Innovative Circuit Probing with AI implement Huang Po-Hao (TeraPower Technology Inc. – Taiwan)

Wafer Level Efficient Characterization and Testing of MRAM Dr. Siamak Salimy (Hprobe – France) and Hantsun Chung (Hermes Epitek – Taiwan)

> **Overcoming Challenges for 5G Production Tests** Dr. Choon Beng Sia (FormFactor, Inc. – Singapore)

Simulation and Verification of FeinProbe Probe Card Model for the 5G WLCSP Application <u>Krzysztof Dabrowiecki</u> and Adrian Lim (Feinmetall GmbH), Jose Moreira (Advantest), Thomas Gneiting and Ali Abdallah (AdMOS), and Paul Hurst (Harbor-Electronics – UK)

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

$\triangleright$

$\triangleright$

$\triangleright$

$\triangleright$

### Friday, October 19, 2018

#### 14:00 to 16:30 – Asia Probing Spotlight

LED Wafer Probe Test Yoichi Funatoko (FormFactor, Inc. – Japan)

Improve the Accuracy of High Speed Simulation to Meet 56G/112G Testing Requirement on PCB Jackie Luo (Shanghai Zenfocus Semi-Tech Co.,Ltd – China)

#### High Performance CIS Wafer Probing using 2D MEMS Technology

Dr. Yunhwi Park, Kyungsub Kim, Youngjin Kim, and Sungjoon Kang (Korea Instruments – Korea) Chang-Hoon Hyun and Kyushik Min (Samsung Electronics. Co. – Korea)

#### Hybrid Type (Mixed Probe Types) Vertical Probe Card

Bryan Lee and James Park (TEPS Co., Ltd – Korea)

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

$\triangleright$

$\triangleright$

$\triangleright$

$\triangleright$

### **Recognition & Awards**

- Best Data Presentation

- Best Overall Presentation

2<sup>nd</sup> Annual SWTest Asia Coming in October, 2019 (will be announced soon!)

### **Thanks for Attending SWTest Asia !**

### We Hope to See you at SWTest San Diego June 2 to 5, 2019 !!!

Rancho Bernardo Inn, San Diego, CA

### **Thanks for your Support !**

### Contact the SWTest Asia Team with any questions

Jerry Broz, Ph.D. General Chair SWTest Asia +1-303-885-1744 E: jerry.broz@swtest.org Clark Liu Asia Technical Program Chair SWTest Asia +886-975-658-563 E: clark.liu@swtest.org

Rey Rincon Technical Program Co-Chair SWTest Asia +1-214-402-6248 E: rey.rincon@swtest.org Maddie Harwood Finance Chair & Conference Management SWTest Asia +1-540-937-5066 E: maddie.harwood@swtest.org E: expo@swtest.org

### **TERMS of SERVICE**

- Information included in the SWTest proceedings and websites reflect the authors opinions and are presented without change. Inclusion in any workshop proceedings (past or present) does not constitute an endorsement by the SWTest, SWTest Asia, IEEE Society, CPMT Society, Computer Society, and/or the Test Technology Council.

- SWTest and SWTest Asia publications and websites contain information that has been provided by exhibitors, sponsors, and authors. Exhibitors, sponsors, and authors are responsible for ensuring that materials submitted for inclusion within the SWTest and SWTest Asia publications and associated sites are accurate as well as in compliance with any applicable laws. SWTest and SWTest Asia does not investigate, edit without permission, or check the accuracy of the submitted materials.

- Papers previously copyrighted or with copyright restrictions cannot be presented. In keeping with a workshop environment and to avoid copyright issues, SWTest and SWTest Asia does not officially seek a copyright ownership or transfer from authors.

- Authors agree by submitting their work that it is original work and substantially not published previously or copyrighted, may be referenced in the work of others, will be assembled / distributed in the SWTest and SWTest Asia Proceedings, and made available for download by anyone from the SWTest and SWTest Asia website.

### Next Generation OSAT - Innovative Circuit Probing with AI implement

#### Scott Huang / 黃柏豪

Product Engineering Div Tel: +886-3-5982828 ext.532700 Mobile : +886-988-620927

Taiwan, October 18-19, 2018

#### Introduction

Al is coming

#### Key system (function) presentation

Opportunity

What we expect

Non-stop & real time production : I-AOI solution

- Technology Application

- Performance & Comparison

Follow on work

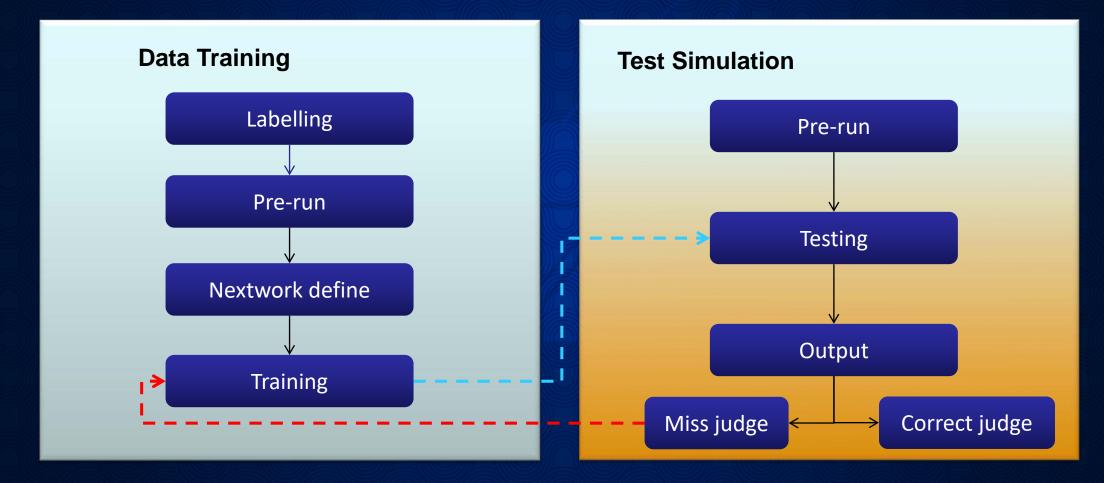

Future development ( Next Generation OSAT )

Industry 4.0 + AI application for manufacture process

Al is Coming !!

## Al is coming, will you join?

#### Attribute of AI (Artificial Intelligence)

Autonomy :

be able to keep working without the direct intervention of humans or event

Reactivity :

be able to perceive current environment and have accurate response

■ Social ability :

be able to interact with other agents (machine) and possibly humans

### **Elements of Al**

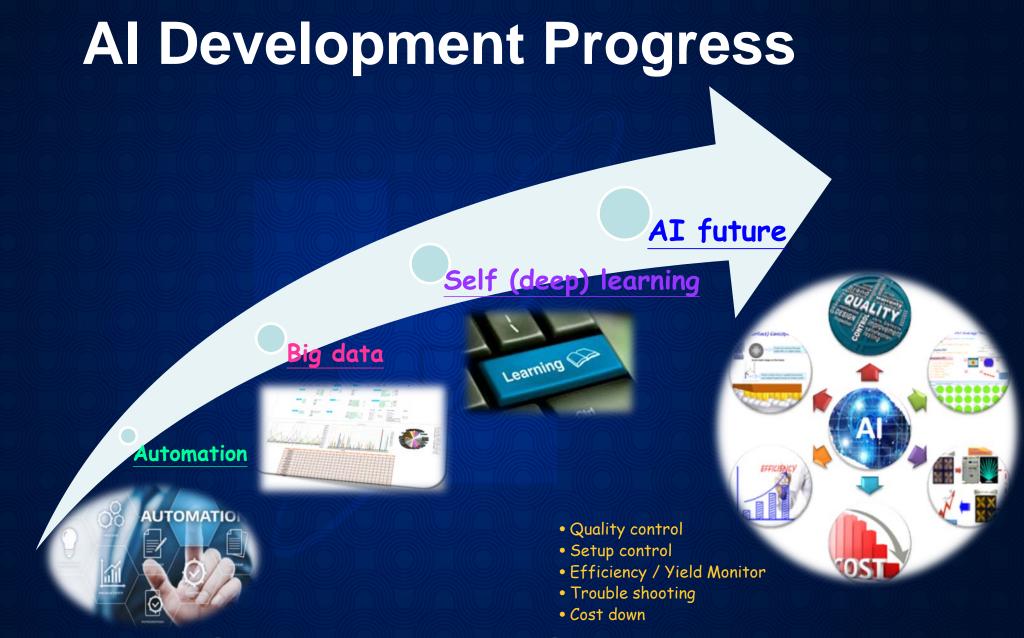

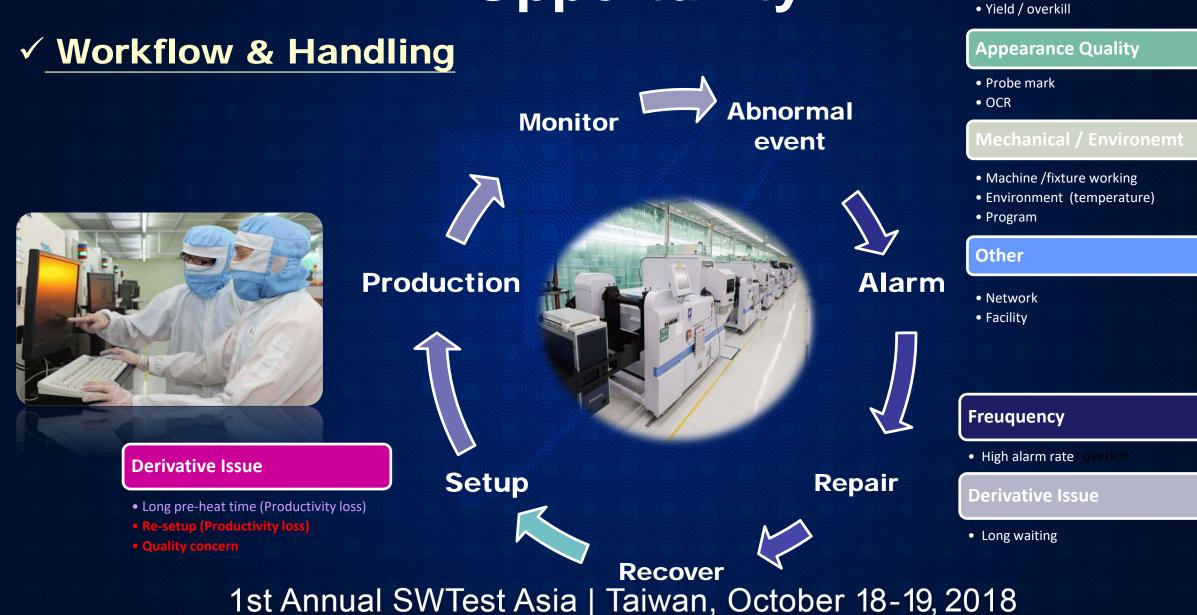

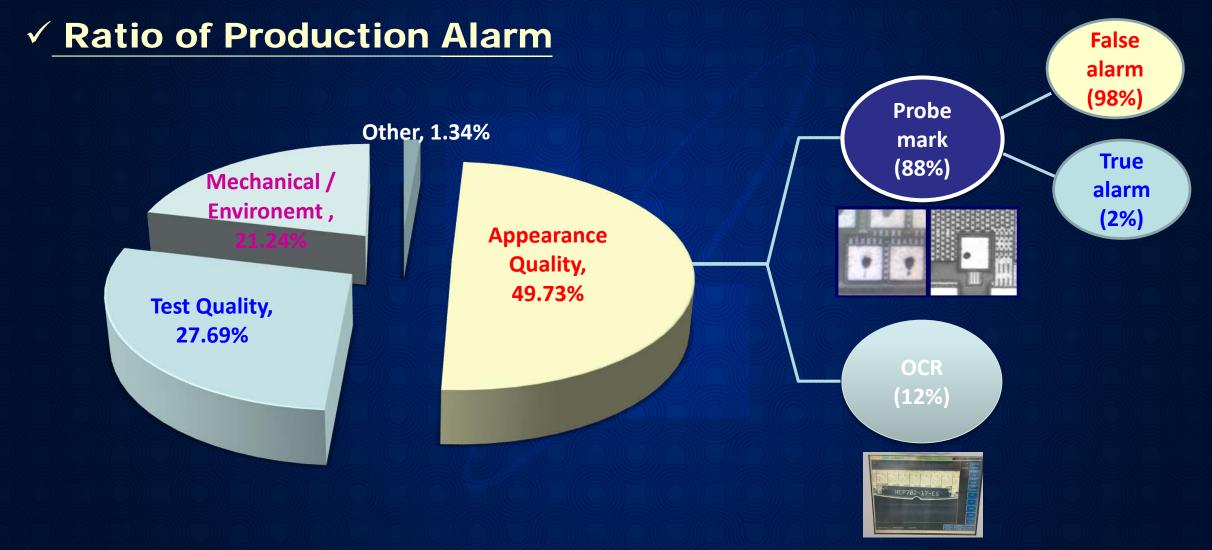

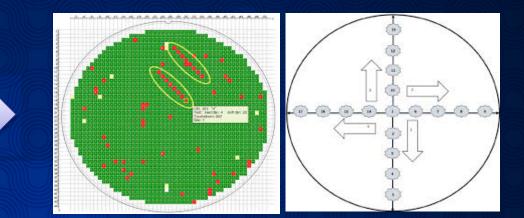

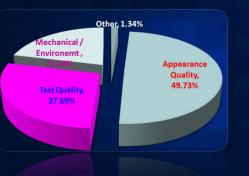

## Opportunity

**Test Quality**

## Opportunity

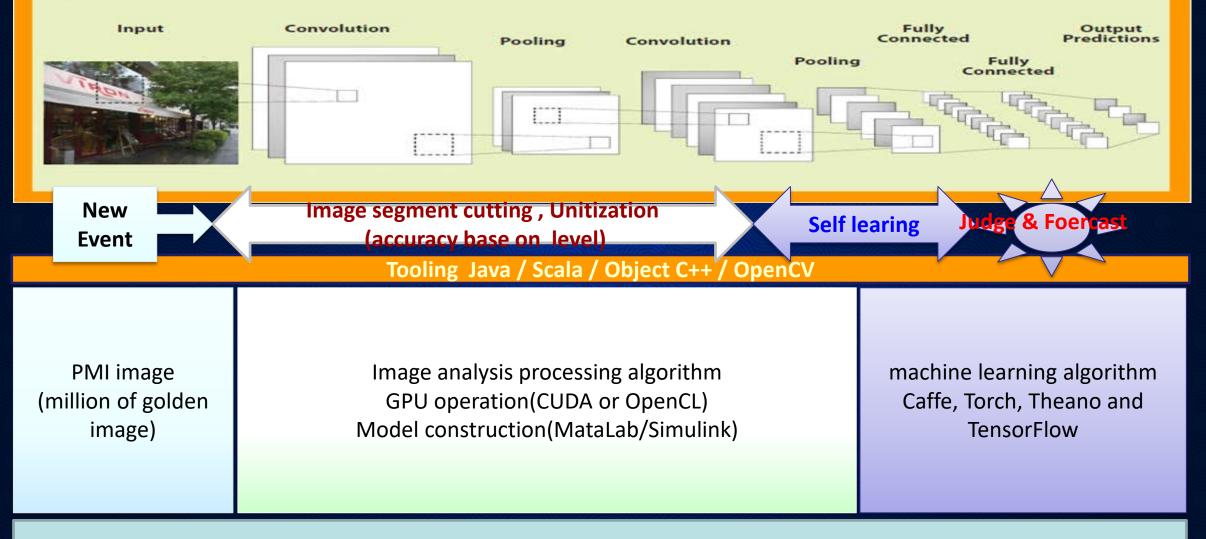

### What we expect !! **Non-stop & Real time Disposition : I-AOI Solution**

As is

#### Manpower support for judgement

- False alarm -> Keep going

- True alarm -> Ask engineer to support

Engineer for trouble shooting (Saving 98% effort due to false alarm)

#### **Artificial Neural Networks Application**

Big Data AnalyticsHadoop / Spark

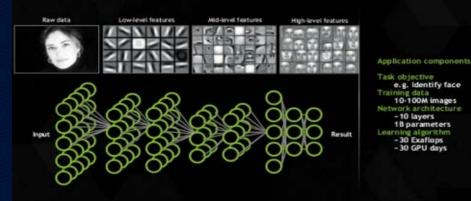

#### **Aritificial Neural Networks**

#### DEEP NEURAL NETWORK (DNN)

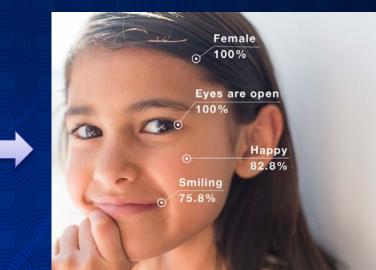

#### **Real-time analysis of behaviors**

yaron / March 16, 2017 / Comments Offon 30 amazing applications of deep learning / Al, Mathematics, Philosophia Naturalis, Writings

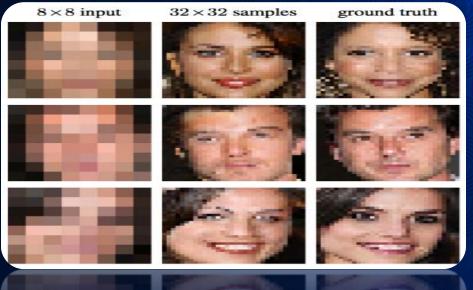

#### **Pixel restoration CSI style**

Nvidia to train 100,000 developers on deep learning AI

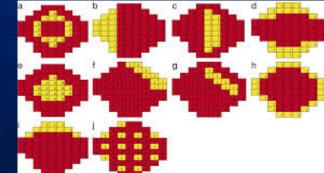

#### Sample Training

#### **Aritificial Neural Networks**

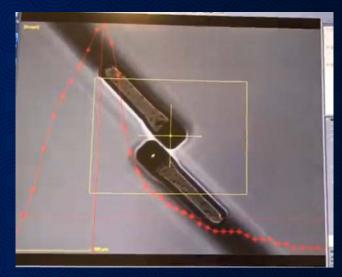

**Object detection (Machine learning)**

#### Judge & Forecast (Find out the target or same one in the database)

#### Feature Recognition (Algorithm analysis)

Similarity comparison(Algorithm analysis)

### **Defect Classification**

Object Detection (machine learning)

#### Judge & Forecast

- 1. Deep Probe Mark (67%)

- 2. Probe mark deviation (28%)

- 3. Incorrect setting of touch down (11%)

Feature identification (Algorithm analysis)

Similarity comparison (Algorithm analysis)

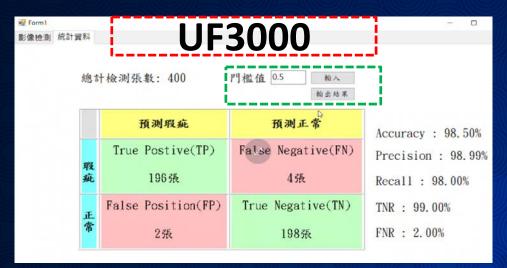

### **ITRI Verify Information (Phase1 – 2018/2/5)**

| ₩ Form1<br>影像檢測 統計算 | 料    | UF3                | <b>DOOEX</b>       |                    |

|---------------------|------|--------------------|--------------------|--------------------|

|                     | 總言   | +檢測張數: 600         | 門檻值 0.5 输入<br>输出结果 | ]                  |

|                     |      | 預測瑕疵               | 預測正常               | Accuracy : 96.67%  |

|                     | 1123 | True Postive(TP)   | False Negative(FN) | Precision : 97.30% |

|                     | 瑕疵   | ▷ 288張             | 12張 🛃              | Recall : 96.00%    |

|                     | 正    | False Position(FP) | True Negative(TN)  | TNR : 97.33%       |

|                     | 常    | 8張                 | 292張               | FNR : 4.00%        |

UF3000 (B/W) Total: 400 Pcs image(Pass 200)(Fail 200) (Fail 200) misjudge→4pcs (Pass 200) misjudge→2pcs

Accuracy Calculate 100 % -{(F4+P2)/(F196+P198)}\*100 =98.5%

UF3000EX (Color) Total: 600 Pcs image(Pass 300)(Fail 300) (Fail 300) misjudge→12pcs (Pass 300) misjudge→8pcs

Accuracy Calculate 100 % -{(F12+P8)/(F288+P292)}\*100 =96.5%

#### ITRI : Industrial Technology Research Institute

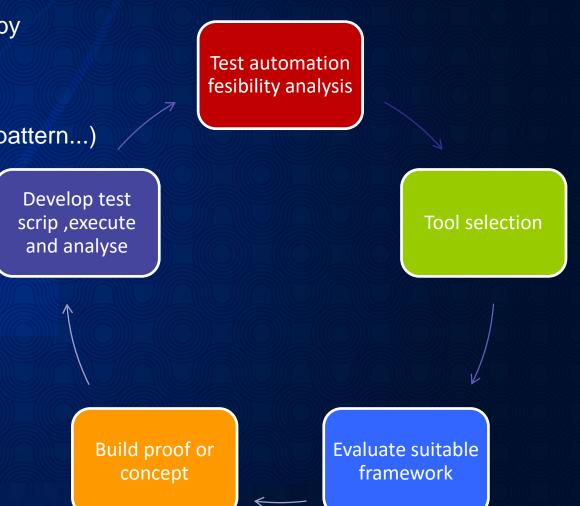

## Application of POC ; Proof of Concept

### **POC** application in IoT :

To make model for behavior of opeation will follow as expection by pciture or deductive method.

- Set operation prototype

- Use chart or image for related technologies (Framework , pattern...)

- Use SW to sminulate the solution and expected result

- Use UML syntax to set sketch of model for solution

## **Color image analysis**

#### Margin Defect

| <u>480.jpg</u> | 3µm |  |

|----------------|-----|--|

| <u>481.jpg</u> | 3µm |  |

| <u>744.png</u>   | Particle touch the line    |   |

|------------------|----------------------------|---|

| 1 <u>747.png</u> | Particle no touch the line | K |

| <u>748.png</u>   | Particle touch the line    |   |

#### Margin & Particle was judged as No defect

#### **Particles defect**

## **Big Data Improves Accuracy Trends**

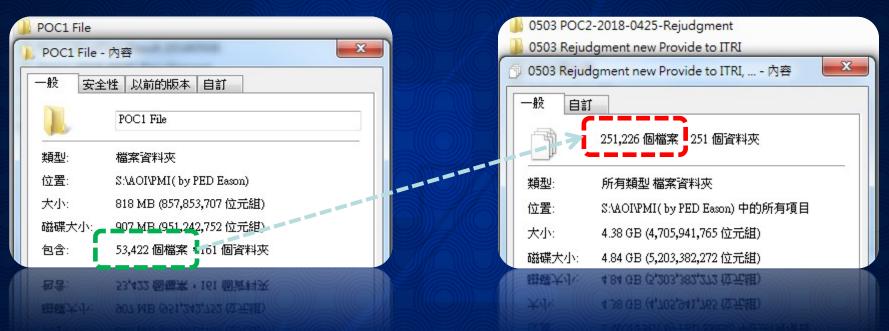

### POC1

#### Increased image data & enhance teaching model

### ITRI Verify Information (Phase2 – 2018/5/8)

#### UF3000 (Black / White Image)

|                            |                        |                                                          | Total. 500 ca imag  | c (or calure)  |                              |

|----------------------------|------------------------|----------------------------------------------------------|---------------------|----------------|------------------------------|

| UF3000                     |                        | Category                                                 | Quantity            | Misjudge       | Classification<br>correction |

| Abnormal                   |                        | Abnormal                                                 | 10                  | 0              | 0                            |

|                            | Judgment & Recognition | Contact IsTooSlight                                      | 0                   | 0              | 0                            |

| ContactIsTooSlight         | Rate                   | DistanceEdge0~3µm                                        | 150                 | 0              | 0                            |

| DistanceEdge0-3um          | 100%                   | No Defect                                                | 0                   | 0              | 0                            |

| NoDefect                   | 10070                  | No Needle Mark                                           | 50                  | 0              | 0                            |

| 🔰 NoNeedleProbeMark        |                        | Particle                                                 | 90                  | 0              | 1                            |

| 🎉 Particle                 |                        | Each Quentity                                            | 300                 | 0              | 1                            |

|                            |                        | Accuracy Calculate                                       |                     | 100%           |                              |

|                            |                        | Reinforce suggestions                                    |                     | Big Data       |                              |

| ///_(((O))/_((O))/_((O))/  |                        |                                                          |                     |                |                              |

| <b>UF3000EX</b>            |                        |                                                          | UF3000EX (Co        | olor Image)    |                              |

| UFSUUUEA                   |                        |                                                          | Total: 700 ea image | (6 Feature)    |                              |

| 1_ContactTooLight          |                        | category                                                 | Quantity            | misjudge       | Classification<br>correction |

|                            |                        | Contact IsTooSlight                                      | 100                 | 2              | 33                           |

| 📕 📕 2_DistanceEdge03micron |                        | DistanceEdge0~3µm                                        | 100                 | 1              | 0                            |

| 3 NoNeedleMark             | Judgment & Recognition | No Needle Mark                                           | 150                 | 0              | 0                            |

|                            | Rate                   | Particle                                                 | 150                 | 0              | 1                            |

| 🖌 📕 4_Particle             | Nate                   | Over the middle waist line                               | 59                  | 6              | 4                            |

|                            |                        | No Defect                                                | 1/1                 |                |                              |

| 5 OverWaistLine            | 98.1%                  | No Defect<br>Each Quentity                               | 141                 | 4              | 79<br>117                    |

| 5_OverWaistLine 6 NoDefect | 98.1%                  | No Defect<br>Each Quentity<br>Judgement Recognition rate | 141<br>700          | 4<br>13<br>1.0 | <u>79</u><br>117             |

ITRI : Industrial Technology Research Institute

### Follow on work

✓ How to enhance accuracy ?

✓ How to enhance the efficiency of AI processing ?

Application for other process ?

### How to enhance accuracy

#### Check item & complexity will impact accuracy of judgement

Check items more will make rigorous condition in feature learning and cause accuracy dropping.

| Check item                       | Database for teching   | Accuracy of judgement |

|----------------------------------|------------------------|-----------------------|

| Particle (粉塵汙染)                  | 2000 ~ 5000 pictures   | 99.8%                 |

| Scratches (刮痕)                   | 2000 ~ 5000 pictures   | 99.8%                 |

| P/M shift (針偏)                   | 2000 ~ 5000 pictures   | 99.8%                 |

| Any two check items              | 10000~ 30000 pictures  | 98%                   |

| Particle + Scratches + P/M shift | 50000~ 100000 pictures | 95%                   |

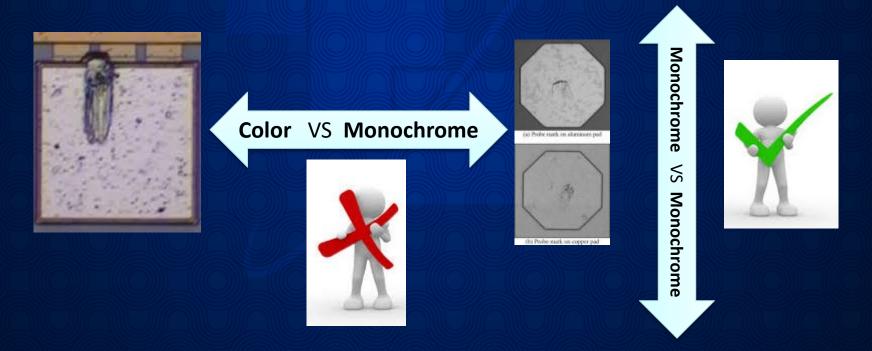

### How to enhance accuracy

Image resolution

color saturation and identification area will impact accuracy of judgement

Pictures from different platform, instrument may have some difference. And it is better to set identification system (including database) by each platform.

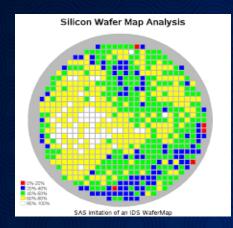

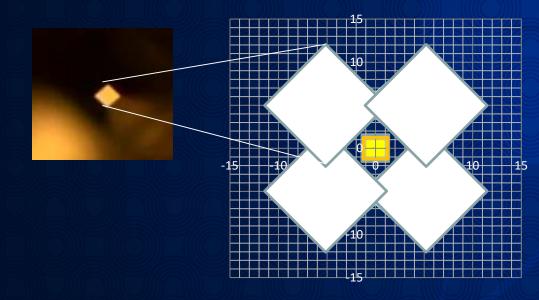

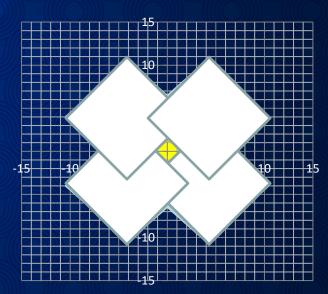

## **Application for wafer map**

Object Detection (machine learning)

Feature identification (Algorithm analysis)

### Map & SUB (Overkill) Analysis

#### **Judge & Forecast**

1. Pass ( 67% )

- 2. Defect Mode I (45%)

- 3. Defect Mode II (23%)

Similarity comparison (Algorithm analysis)

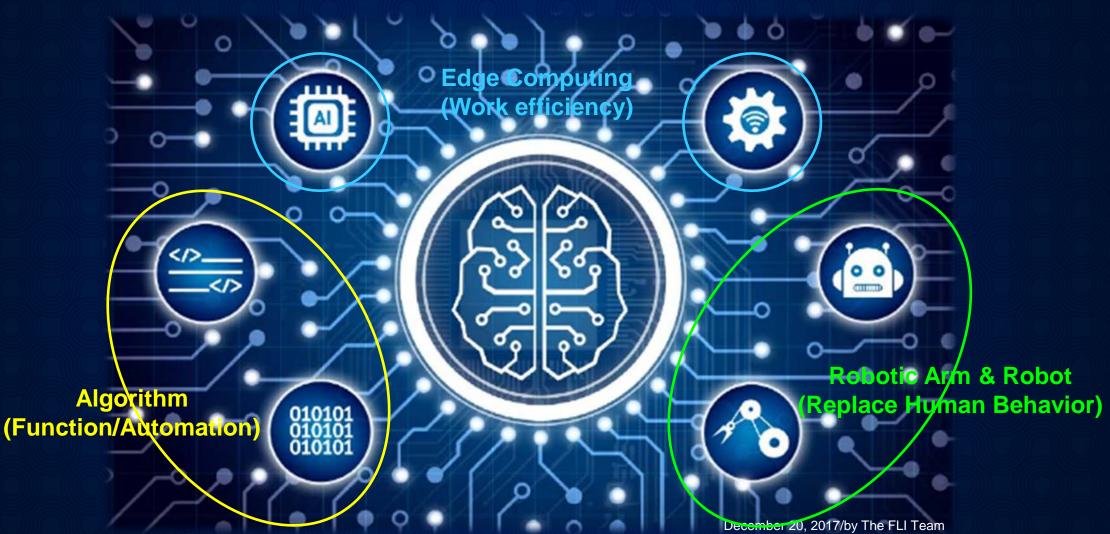

### Future Development (<u>Next Generation OSAT</u>)

- Integration of different technologies (Image Technology, Algorithm, Edge Computing, Robotic Arm & Robot) for innovation testing

- It is not pipe dream to dramatically drop production loading by Al development

- Industry 4.0 + AI will make real time & most efficient in production (Smart Manufacture)

- Quality level will keep enhancing due to real time disposition & less manual operation

- ✓ Accurate forecast make more benefit for enterprise

### **Elements of Al**

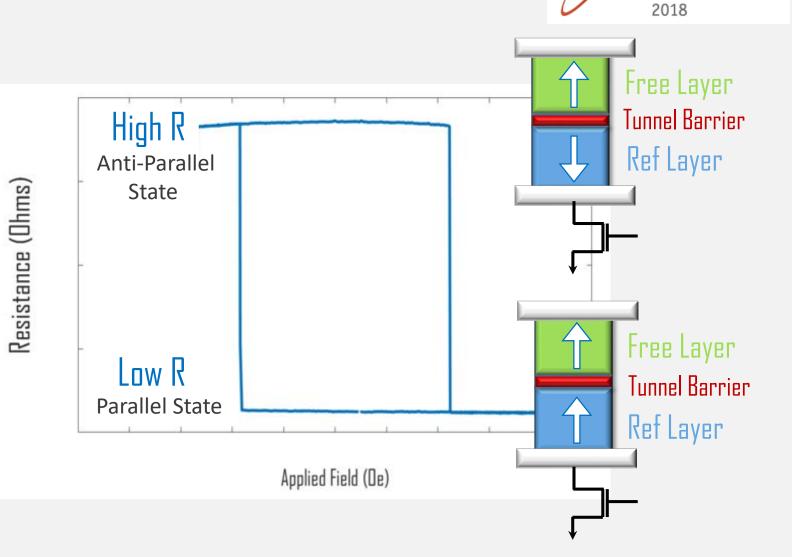

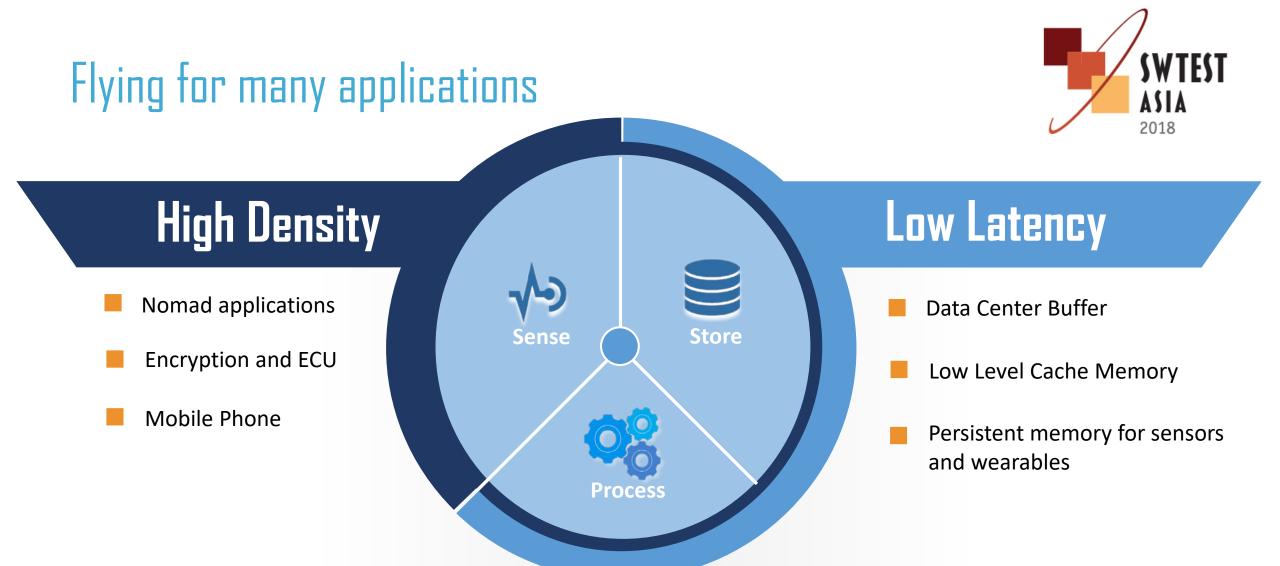

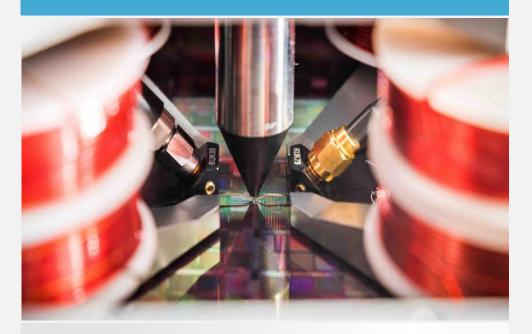

### Wafer Level Efficient Testing of MRAM

Siamak SALIMY, Ph.D. – Chief Technical Officer

Hantsun CHUNG – Sales & Application Manager

Taiwan, October 18-19, 2018

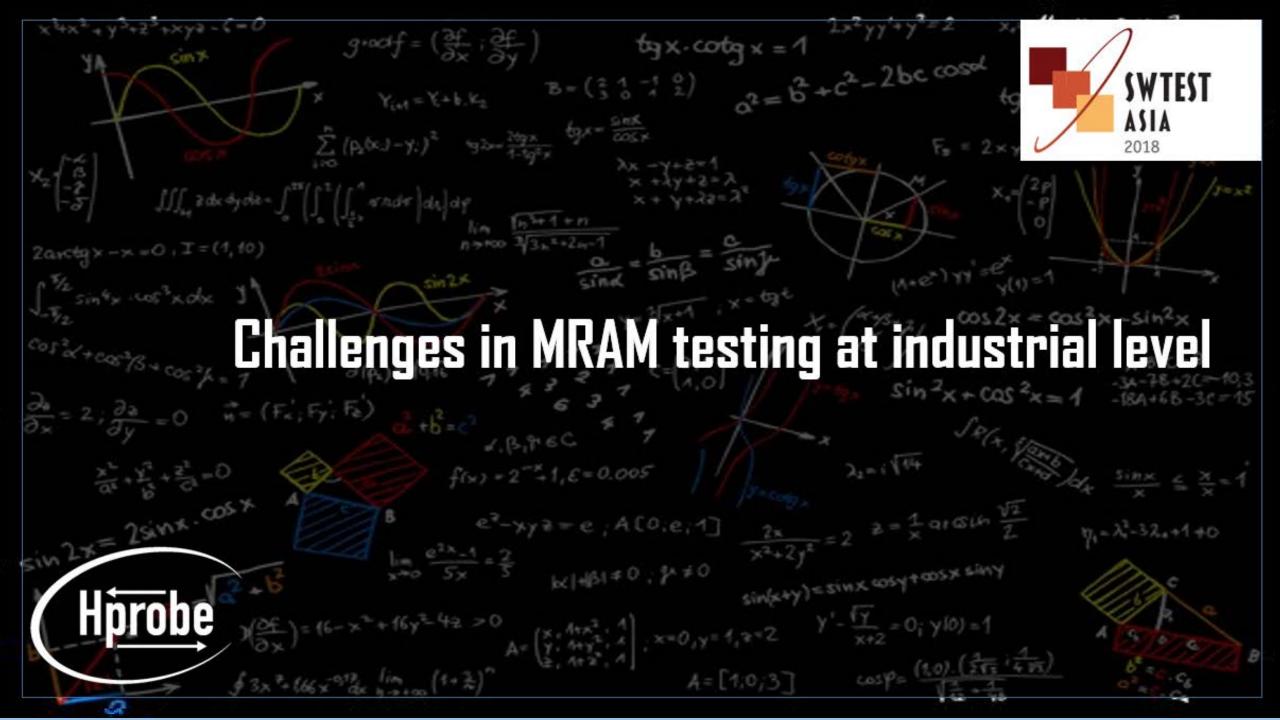

### The top class properties of MRAM

High Performances: DRAM like write perf.

Non-Volatile

- Fast Read/Write : DRAM&SRAM like

- Scalable at low technology nodes

- Data requires no refresh

Bi-state magnetic device Switching with current pulses

ASIA

Hirobe S. Salimy, H. Chung

Driven by Internet of Things, Artificial Intelligence and Big Data

# Overview

## Magnetic Automated Test Equipment

Hprobe

S. Salimy, H. Chung

| <b>3</b> D | Magnetic Generator | High Field Amplitude<br>Ultra-Fast Sweeping |

|------------|--------------------|---------------------------------------------|

| MTJ        | Parametric Tester  | MRAM<br>Sensors                             |

|            |                    |                                             |

| SoC        | Functional Tester  | Full ATE integration<br>Memory Tester       |

Clients

## Foundries

## **Integrated Device Manufacturer**

## **Original Equipment Manufacturer**

Research Lab and Institute

## From Development To Production

**Testing Time** Device Characterization Full Set of Parameters Extensive Test Coverage Multi-Test Sequences

Development

**Device** Testing

**Capability Analysis**

**Corner Evaluation**

SPC limits definition

Wafer Sorting

Manufacturing Yields

**Reduced Test Coverage**

#### Production

The specificity of MRAM require testing under magnetic field in all phases

Qualification

Hprobe

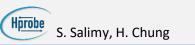

## How to test MRAM devices ?

#### **Under Magnetic Field**

- Sweeping Magnetic field in perpendicular direction up to 0.5 Tesla (FL switching)

- Extracting the switching field, switching probability and energy barrier

Challenge: High Field with Fast Amplitude Sweeping

#### With Ultra Narrow Voltage Pulses

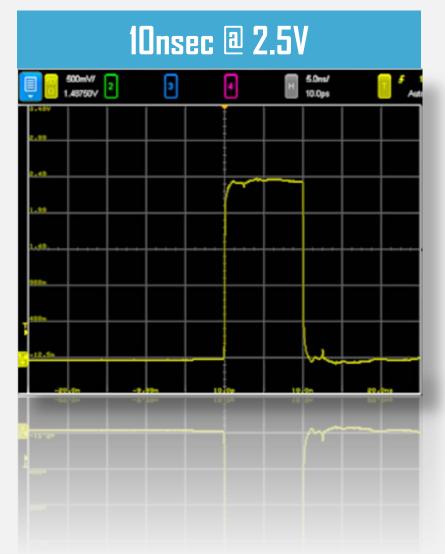

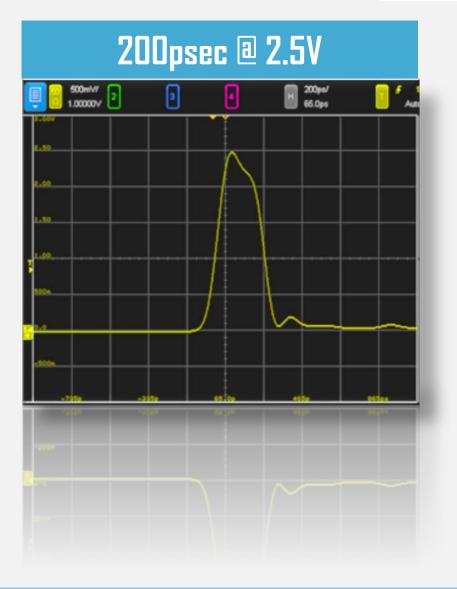

- Sweeping Voltage Pulsed Amplitude down to 200psec at 2.5V

- Extracting the switching probability vs pulsing parameters

Challenge: Sweep Fast Amplitude of Ultra-Narrow Pulse Width

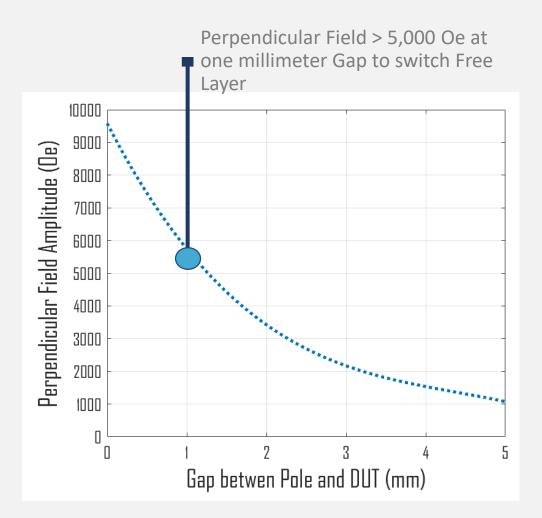

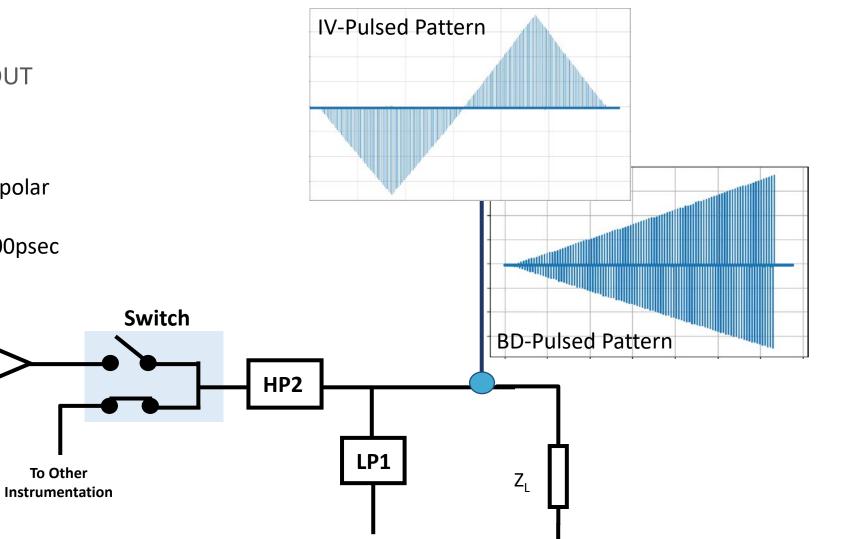

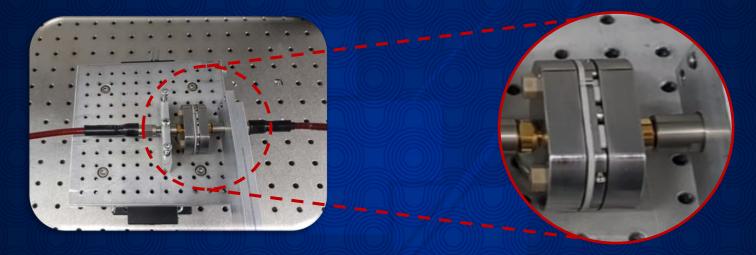

## Proposed Setup for MRAM Parametric Testing

- RF path down to the probe on pulsing side

- Probing done by 2/4 point probes measurements **Magnetic Field Control** 3D Magnetic Generator Source/Sense Control AWG Filter ٨٨٨ ...... MTJ V/I**Pulsing Control** .... RF amp + Filters Pulse/AWG Л

# **3D Magnetic Generator TM**

$\vec{\nabla} \cdot \vec{D} = \rho$  $\vec{\nabla} \cdot \vec{B} = 0$

$\vec{\nabla} \times \vec{H} =$

ðB

$\vec{\nabla} \times \vec{E} = -\partial t$

## Magnetic Field Generation

|                    | Supra<br>conductors | Standard<br>Coils | Permanent<br>Magnets | Hybrid Ferro<br>Magnets + Coils |

|--------------------|---------------------|-------------------|----------------------|---------------------------------|

| Field<br>Amplitude | HIGH                | LOW               | LOW                  | HIGH                            |

| Sweep Speed        | LOW                 | HIGH              | LOW                  | HIGH                            |

| Heating            | HIGH                | HIGH              | LOW                  | LOW                             |

## Hprobe Magnetic Generator <sup>TM</sup>

Full 3D Magnetic Field

- Single Axis Field

- Rotating Field

- Perpendicular Field up to 750mT

- Planar Field up to 350mT

- No liquid cooling system

## **Unique Patented Design**

Controllable Field Over the 3 Directions of Space

## Out of Plane Field

## **Perpendicular Configuration**

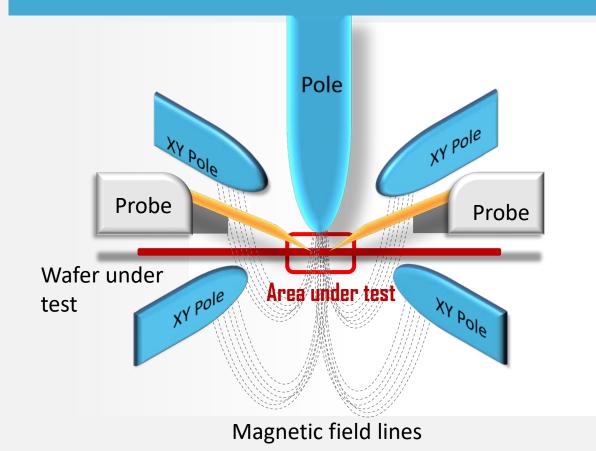

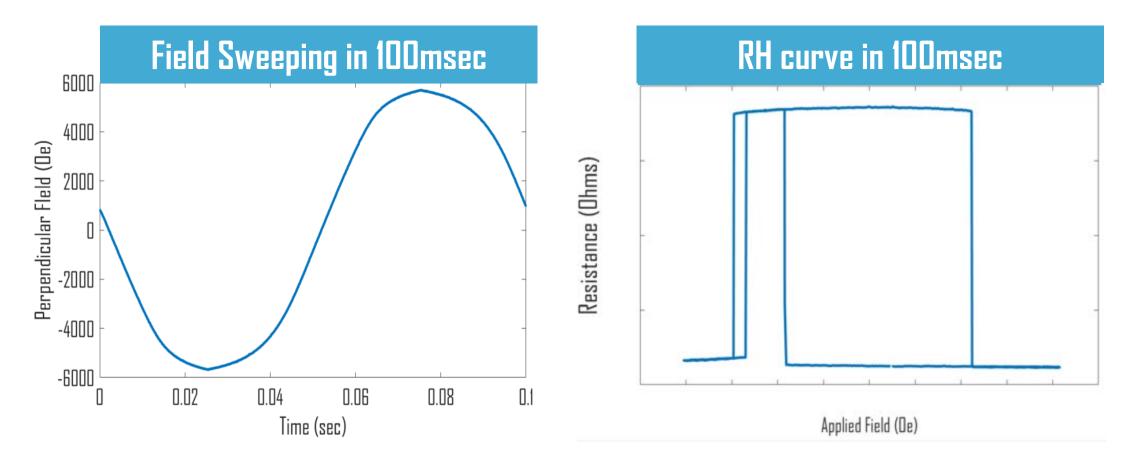

## Fast Field Sweeping Capability

Variable Sweeping Rate

Synchronized Measurement of MTJ resistance at each field steps

Fast sweeping in any field configuration

## Ultra-Fast Field Sweeping

Full R-H sweeping curve in down to 50msec per MTJ

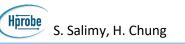

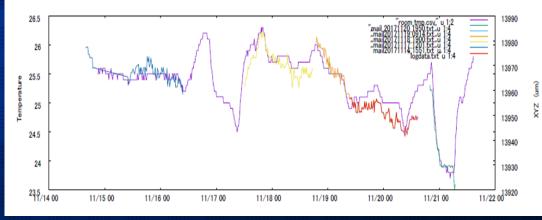

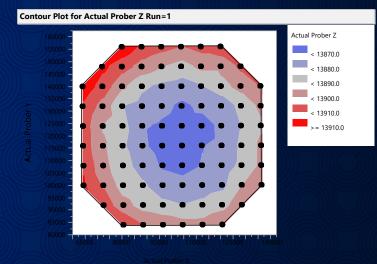

## Temperature

# **RF Ultra Fast Pulsing Channels**

## Options To Generate Ultra-Narrow Pulsed Width

|                 | Pros.                                   | Cons.                                                                                              |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------|

| Pulse Generator | Amplitude > 2.5V Bipolar on 50Ω<br>load | No sweep Amplitude Capability<br>Need to activate mechanical relay at<br>output to sweep amplitude |

| RF AWG          | Ultra-Fast Amplitude Sweeping           | Amplitude Limited to <+/-1V on 50Ω<br>load                                                         |

|                 |                                         |                                                                                                    |

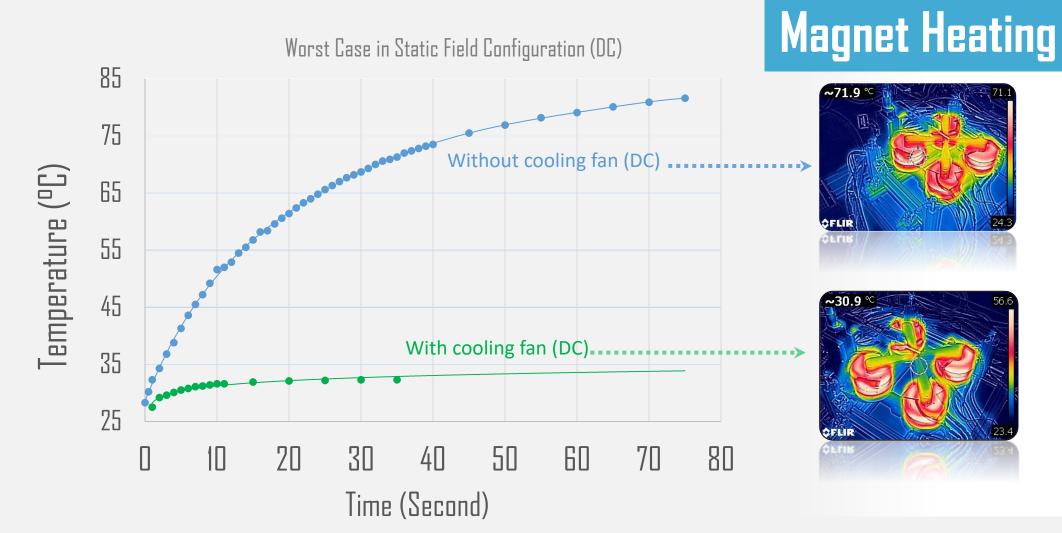

## Choice of RF ultra-Fast AWG

Design of the RF path down to the DUT

Bandwidth > 6 GHz

HP1

Ve

AWG

- Amplitude of +/-2.5V Bipolar

- Pulse Width down to 200psec

G

....

To sense channel

$Z_g$ =50  $\Omega$

H<u>probe</u>

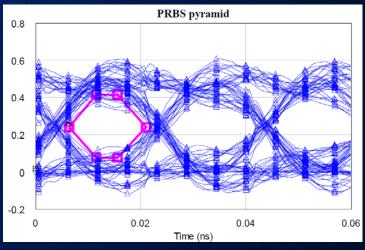

## Pulsed Shape at PW of 10nsec and 200psec

#### Designed of a Test System for wafer level testing under magnetic field for MRAM devices

- With High perpendicular field (>500mT) and ultra-fast sweeping capability 10kSa/sec

- Large bandwidth, fast amplitude sweeping and pulsing capability down to 200psec

- Compatible with all phases from development to production of integrated magnetic devices

## Speed Up Magnetic Testing

## Thank You

Gilles ZAHND Eric MONTREDON Nathalie LAMARD Brice BLANC Yann RICHARD Laurent LEBRUN Jean-Pierre NOZIERES

-

-

Isabelle JOUMARD Antoine CHAVANT Ricardo SOUSA

Lambert LAIElva CHANG

#### Taiwan, October 18-19 2018

## **Overcoming Challenges for 5G Production Tests**

Taiwan, October 18-19, 2018

## Overview

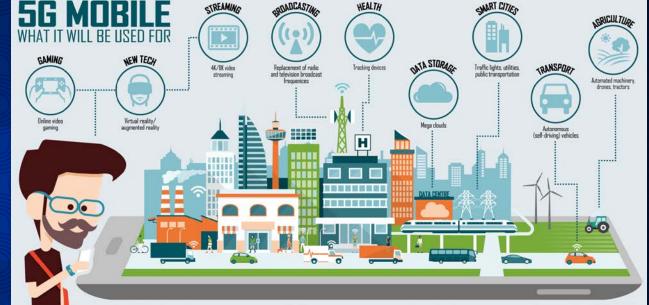

- What is 5G?

- Economic Impacts of 5G

- Key Challenges for 5G Production Tests

- Handling Large Number of RF Test Channels

- Ensuring Excellent Signal Integrity

- Possible Solutions

- In-membrane Antenna OTA Tests

- Dedicated Calibration Substrate & Power Calibration

- Summary

- Acknowledgements

Choon Beng Sia Ph.D. 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## What is 5G?

- Communication Network for 4<sup>th</sup> Industrial Revolution

- 5G RF, Optical, High Speed Digital

- Extremely Fast Data Rates

- 10Gbps (5G) vs 100Mbps (4G)

- Ultra Low Latency

- 1ms (5G) vs 50ms (4G)

- Huge No. of Connections

100 billion (5G) vs 1000 (4G)

- Higher Energy Efficiency

- Always Stay Connected

- Connect Everyone, Everything

#### **5G NETWORK ARCHITECTURE**

#### 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Choon Beng Sia Ph.D.

Sources: https://www.quora.com/What-is-5G-Will-5G-technology-bring-new-dimensions-to-wireless; http://www.emfexplained.info/?ID=25916; https://en.wikipedia.org/wiki/Fourth\_Industrial\_Revolution

## **5G Use Cases**

#### Enhanced Mobile Broadband

Enterprise/Team Collaborations, AR/VR, Enhanced Wireless Broadband, Education, Mobile Computing, Enhanced Digital Signage.

#### Massive Internet of Things (MIoT)

Choon Beng Sia Ph.D.

Smart Cities, Energy/Utility Monitoring, Asset Tracking, Smart Agriculture, Physical Infrastructure, Smart Homes, Remote Monitoring, Beacons & Connected Shoppers.

- Mission Critical Services (Low Latency Requirement)

- Autonomous Vehicles, Remote Patient monitoring/TeleHealth, Industrial Automation, Smart Grid, Drones.

- 4G braking command makes a car at 100kmph to stop after 1.4m.

- 5G Same car stops within 2.8cm due to ultra low latency.

#### 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Source: The 5G Economy: How 5G Technology will contribute to the Global Economy, Jan 2017 for Qualcomm https://www.independent.ie/business/technology/news/the-need-for-speed-is-ireland-ready-for-5g-the-next-big-thing-in-cellular-technology-36629260.html

## **Economic Impacts of 5G (USA)**

- 5G → 3 million jobs, US\$275B investments, US\$500B economic growth

- Smart Cities

- US\$160B in savings  $\downarrow$  Energy Use &  $\downarrow$  Congestion.

- Eg. Sensors monitor Health & Safety of critical infrastructure Buildings, Roads & Bridges.

#### Transportation

- Self-driving cars  $\downarrow$  90% emissions,  $\downarrow$  40% Travel Time & Save 22,000 lives annually.

- 5G will save US\$450B annually in transportation costs.

#### • Healthcare

- Remote Patient Monitoring & Surgery through connected healthcare devices

- US\$305B in Healthcare Cost-savings Annually.

- Energy

- 5G allow Energy Grid to be more Accurately Monitored, Improving Management, Reducing Costs, adding US\$1.8 trillion in revenue to the U.S. economy.

#### Choon Beng Sia Ph.D. 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

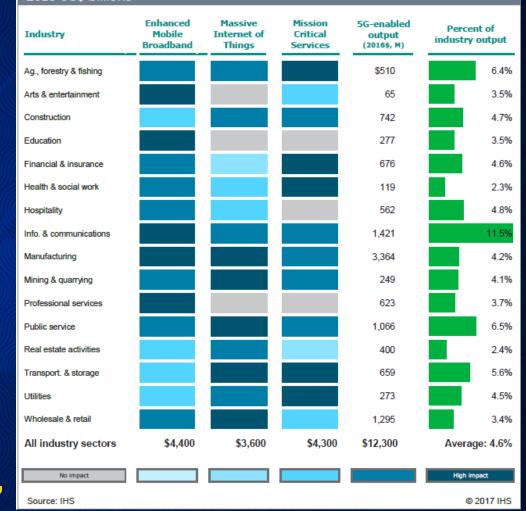

## **Economic Impacts of 5G (World)**

#### Global 5G value chain output and employment in 2035

- By 2035, Value Chain US\$3.5T, 20M Jobs

- CEO Qualcomm, "5G Impact similar to Introduction of Electricity or Automobile"

Choon Beng Sia Ph.D.

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

5G will enable \$12 trillion of global economic activity in 2035 2016 US\$ billions

Source: Prepared by IHS, The 5G Economy: How 5G Technology will contribute to the Global Economy, Jan 2017 for Qualcomm Inc.

## **Global Race to 5G**

- 5G Readiness Index

- Spectrum Availability

- Infrastructure Planning

- CTIA, consortium representing U.S. **Wireless Communications** Industry

- 250 companies

Choon Beng Sia Ph.D.

**5G Readiness Index**

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

9<sup>th</sup>

10<sup>th</sup>

C:

ingapor

## **Global Race to 5G**

- 2020 appears to be commercialization target for 5G

- Focus on Sub-6GHz, Expect Challenges in mmW Tests

#### Choon Beng Sia Ph.D. 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Source:- Keysight World 5G Presentation, Shanghai June 2018

## **5G Field Trials**

# WINDLE Y HERRE INCREMENTATION Russia will stream the World Cup in VR with 5G SHARE Image: Comparison of the stream SHARE Image: Comparison of the stream

#### • Intel & NTT Docomo 5G Trial at Japan 2020 Summer Olympics:

- 8k 360 degree video streams

- 5, 24-28, 37-40, 64-71 GHz Proposed

## Intel makes huge 5G promises for the 2020 Olympics

6

The Tokyo games will be awash in 5G.

Devindra Hardawar, @devindra 02.25.18 in Internet

nts Shares

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## **Requirements for 5G Production Tests**

#### New Test Equipment Needed

- Higher Test Frequencies (> than most ATE testers can handle)

- Very Large Number of Channels

#### Short Time of Test with High Throughput

Parallel test (multi-site)

#### High Accuracy is needed to Validate Performance

- Good Signal Integrity at high RF frequency

- Prevent packaging bad devices due to yield

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## **Key Challenges in 5G Production Tests**

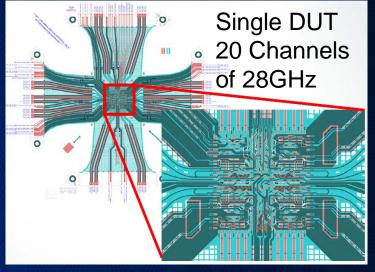

- 1. Handling Very Large Number of RF Test Channels

- Parallel Tests require even larger no. of Channels in RF Tester = \$\$\$\$

- Challenges in Routing RF Channels in Parallel Test setup (X8 DUT, >160 Channels, >25GHz)

#### 2. Ensuring Excellent Signal Integrity

- Post-Calibration Verifications & Use of Dedicated Calibration Standards Substrates.

- Maintaining Calibrated State for as long as possible (esp. with Frequency Extenders).

- Throughput impact if frequent recal. needed.

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## 1. Handling Very Large Number of RF Test Channels

- 5G is using higher freq.

- Larger Attenuation at Higher Frequencies.

- Omnidirectional Antenna cannot support

- Directional Antenna needed

- Active Phased Arrays & Beamforming

- Up to 64 lines at 70 GHz in a single device

- Massive MIMO with Active Phased Array Antennas for 5G.

Choon Beng Sia Ph.D. 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## 1. Handling Very Large Number of RF Test Channels

| Test Method                      |  | Advantages                                                       | Disadvantages                                                                                                                     |

|----------------------------------|--|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Full<br>Channel                  |  | <ul><li>Full RF Coverage</li><li>Fast</li></ul>                  | <ul> <li>Expensive Tester</li> <li>Routing/Space Transformation<br/>Difficulties</li> </ul>                                       |

| Balun,<br>Switches,<br>Combiners |  | <ul> <li>Established<br/>Methods</li> </ul>                      | <ul> <li>Discrete Components – High<br/>Loss, Large &amp; Bulky</li> <li>On-ProbeCard – Narrowband &amp;<br/>High Loss</li> </ul> |

| Antenna<br>Coupling              |  | <ul> <li>Reduce Channel<br/>Count (4:1<br/>combining)</li> </ul> | <ul> <li>Loss than Conducted Tests</li> <li>Space needed for Antenna</li> </ul>                                                   |

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

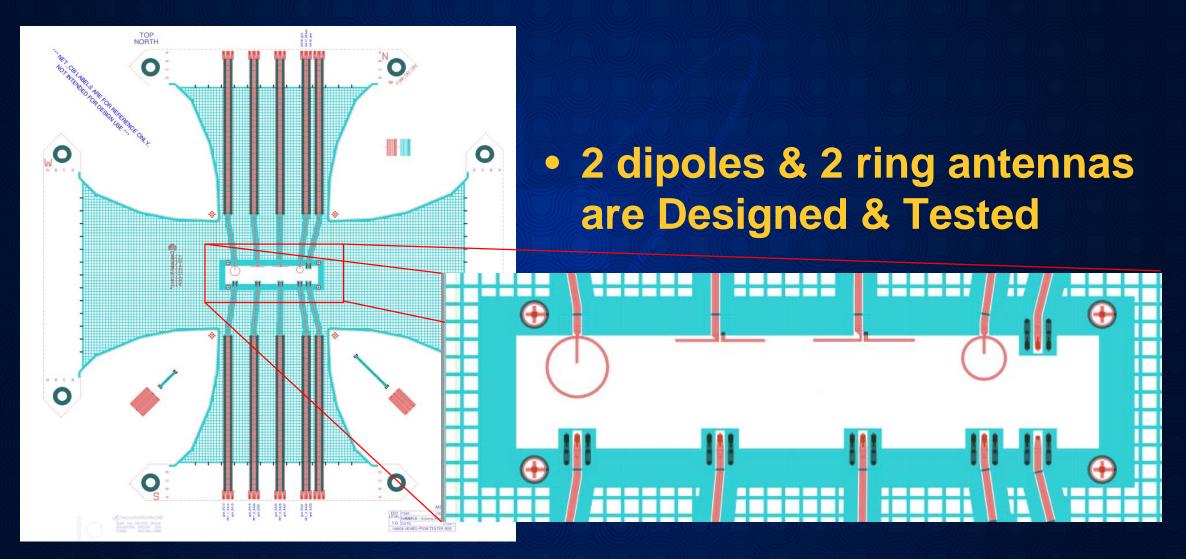

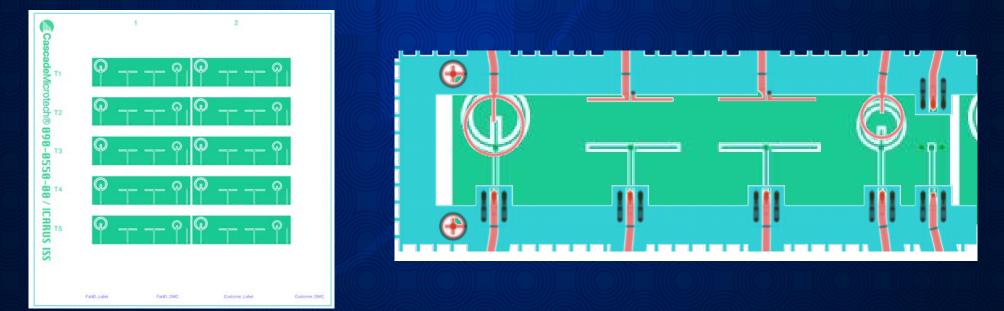

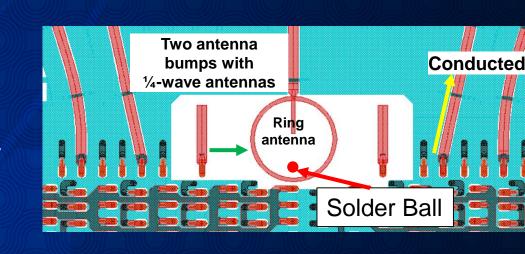

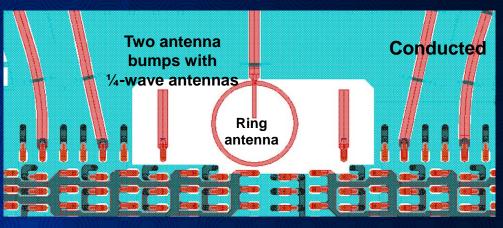

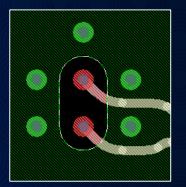

### Membrane Probe Head & Antenna Test Structures

h.D. 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## **Ceramic Substrate for Reception Tests**

- A substrate was fabricated for reception of the signals.

- Signal goes back to the probe head (membrane) through GSG tips.

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

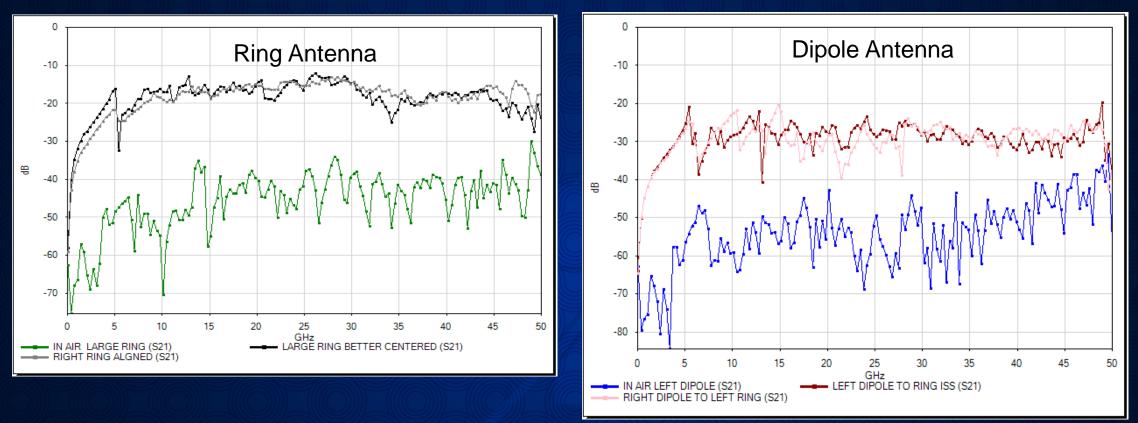

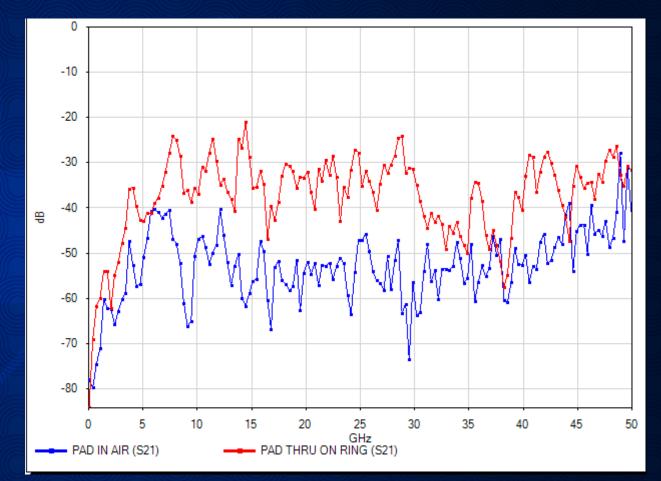

## **Insertion Loss for Ring & Dipole Antenna**

- Insertion Losses higher than noise by about 20dB.

- Wide bandwidth observed due to near field coupling (>100µm).

- Ring Antenna has better performance than Dipole Antenna.

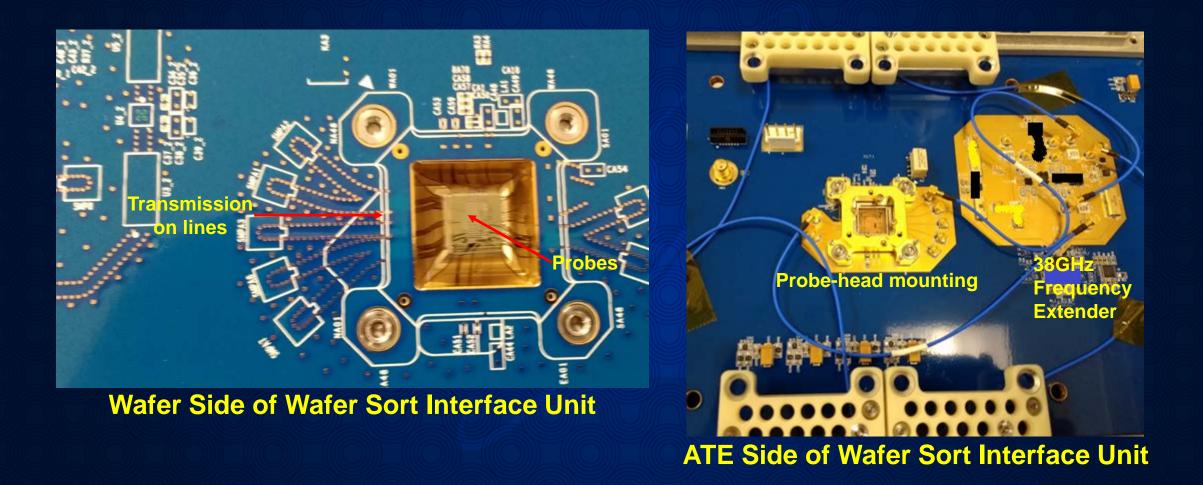

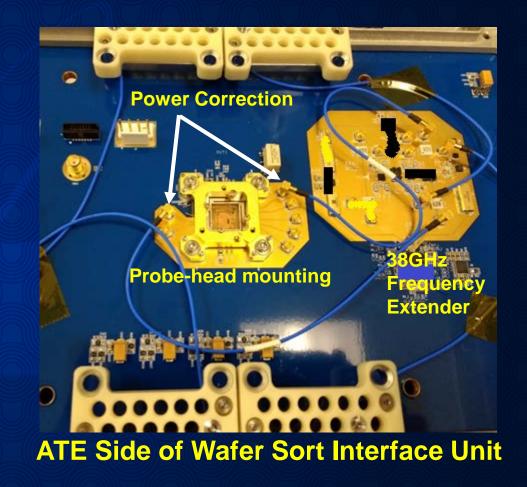

## Intel's ATE mmW Test Setup

- Advantest 93000 PSRF ATE System

- generates 6 GHz for device testing

- SIU PCB (Wafer Sort Interface Unit)

- mmW Frequency Extender developed using off-the-shelf components.

- Up-converts RF Test Signal from the ATE  $\rightarrow$  38 GHz CW signal.

- Down-converts 38 GHz RF signal from the DUT to a signal manageable within the measurement range of the ATE (< 6GHz)</li>

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

SW Test Workshop, June 3-6 2018, USA

### Intel's ATE mmW Tests – Membrane Probe Head

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

SW Test Workshop, June 3-6 2018, USA

Choon Beng Sia Ph.D.

## Intel's ATE mmW Test – Test Setup

#### Fully Conducted Test

Electrical contact

- ¼ wave Antenna Transmitting to Ring Antenna

- -1/4 wave makes contact with solder ball and then transmits to ring antenna

- Solder Ball Transmit to Ring Antenna

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

SW Test Workshop, June 3-6 2018, USA

## Intel's ATE mmW Test – Results

| Probe     | Transmit Power from Same DIE (dBm) |                          |                      |  |

|-----------|------------------------------------|--------------------------|----------------------|--|

| touchdown | 1/4λ to Ring Antenna               | <b>Ring Antenna only</b> | Fully Conducted Path |  |

| 1         | -63.27                             | -86.67                   | -38.593              |  |

| 2         | -63.169                            | -85.95                   | -38.594              |  |

| 3         | -63.8                              | -86.68                   | -38.588              |  |

| 4         | -63.825                            | -86.62                   | -38.589              |  |

| 5         | -63.636                            | -85.63                   | -38.59               |  |

| 6         | -63.687                            | -85.51                   | -38.597              |  |

| 7         | -63.793                            | -86.62                   | -38.602              |  |

| 8         | -64.043                            | -86.23                   | -38.61               |  |

| 9         | -64.728                            | -85.14                   | -38.616              |  |

| 10        | -64.673                            | -85.98                   | -38.615              |  |

| 11        | -64.955                            | -86.69                   | -38.634              |  |

| 12        | -64.866                            | -85.43                   | -38.649              |  |

| 13        | -65.111                            | -85.95                   | -38.648              |  |

| 14        | -65.785                            | -84.65                   | -38.698              |  |

| 15        | -65.826                            | -84.25                   | -38.711              |  |

| 16        | -65.854                            | -84.13                   | -38.757              |  |

| 17        | -65.748                            | -84.32                   | -38.762              |  |

| 18        | -65.831                            | -84.61                   | -38.766              |  |

| 19        | -65.696                            | -84.21                   | -38.753              |  |

| 20        | -65.692                            | -84.74                   | -38.778              |  |

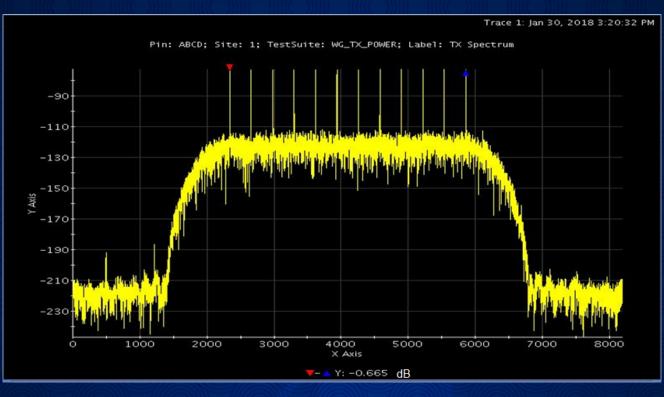

mm Wave Probe Connection: 2 to 1 combining with ¼-wave antennas

#### Very Repeatable Measurements at 38.56 GHz

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

SW Test Workshop, June 3-6 2018, USA

Choon Beng Sia Ph.D.

## Intel's ATE mmW Test – Results

Spectrum measured with the ¼-antenna

Choon Beng Sia Ph.D

- Multi-tone Spectra at 38 GHz using an IQ waveform (modulated signal)

In-membrane Antennas is feasible for 5G Production Tests.

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

SW Test Workshop, June 3-6 2018, USA

## 2. Ensuring Excellent Signal Integrity

- Post-Calibration Verification Checks are strongly recommended

- It is the only way to reveal Calibration Anomalies

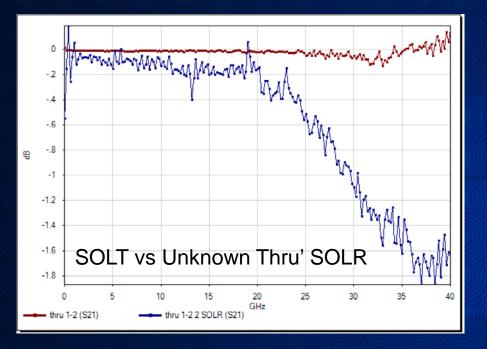

- SOLT vs SOLR on thru', SOLT appears better

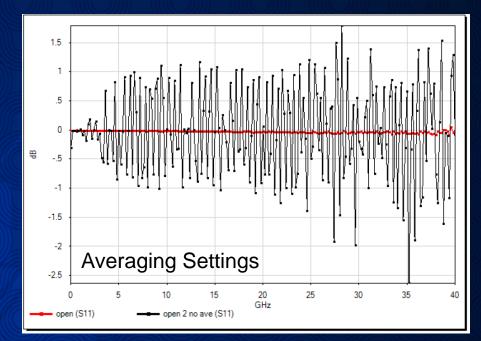

- Open check with Gain (Optimize with IFBW settings)

## **Dedicated Calibration Standards**

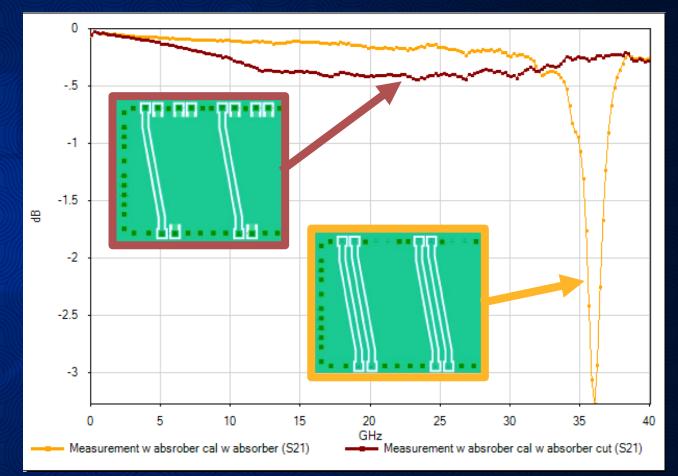

- Dedicated Calibration

Substrates for 5G

- Higher Test Frequencies

- Narrow Pitch GSSG Layout

- Results in 36 GHz resonance for Thru' standards.

- Calibration fail at 36 GHz.

- Adjacent thru' removed improves calibration performance.

- Experience & Know-How are Critical.

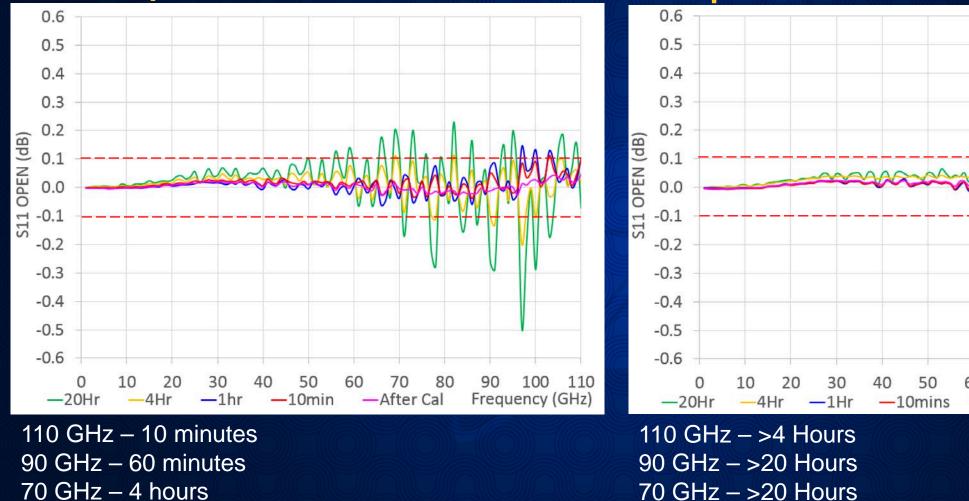

## **Post-Calibration System Stability**

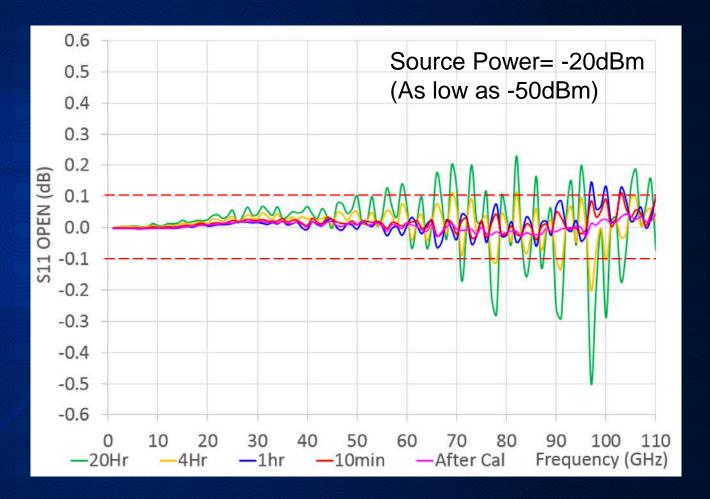

- As Freq ↑, System Post-Calibration Stability↓.

- Worse off when Freq. Extenders are used.

- Eg (67-110 GHz Extender)

- Open is a Convenient Check.

- Open After Cal. (< ±0.1 dB).</li>

- 110 GHz 10 minutes

- 90 GHz 60 minutes

- 70 GHz 4 hours

- Re-calibration is required & Throughput ↓.

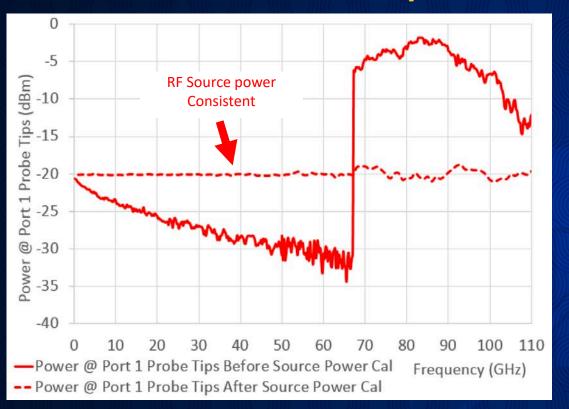

## **Power Calibration with Frequency Extenders**

- Power Cal. not perform on Intel Test Results but if ATE supports...

- Source Power Cal.

- Characterize Actual Source Power after Frequency Extenders with Power Meter.

- Account for the Losses of Probecard.

- Perform Source Power Correction from instrument to probe tips.

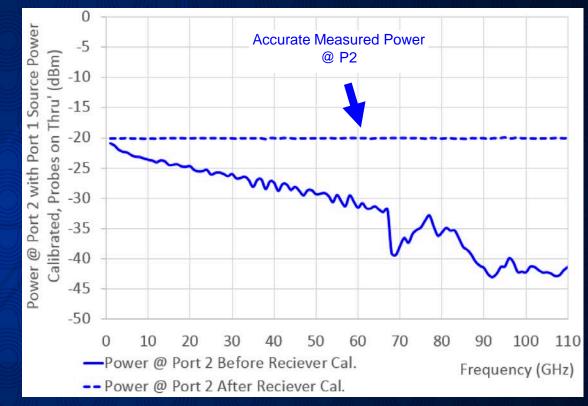

- Receiver Power Cal.

- Put Probe Head on Thru' Standard.

- Perform Receiver power Correction to Probe Tips.

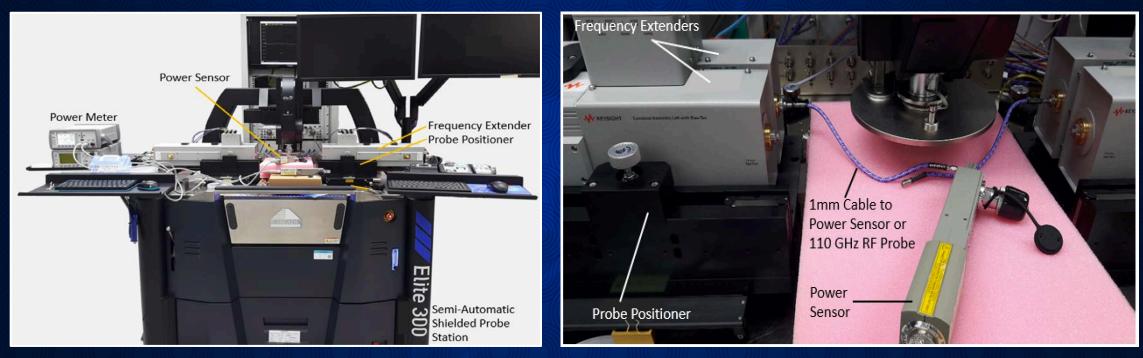

## **Power Calibration with Frequency Extenders**

#### 110 GHz Engineering Setup for 5G Device Characterization

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Choon Beng Sia Ph.D.

## Power Calibration with Frequency Extenders Source Power @ Tips Measured Power @ P2 Receiver

- Before Cal. Loss ↑ with freq. & freq. extender Influence power settings.

- After Cal. Consistent Source Power.

- Before Cal. Huge Losses at Receiver

- After Cal. Consistent Power of -20 dBm regardless of freq.

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Choon Beng Sia Ph.D.

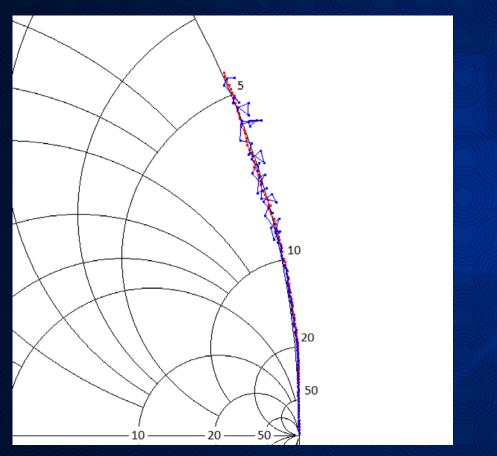

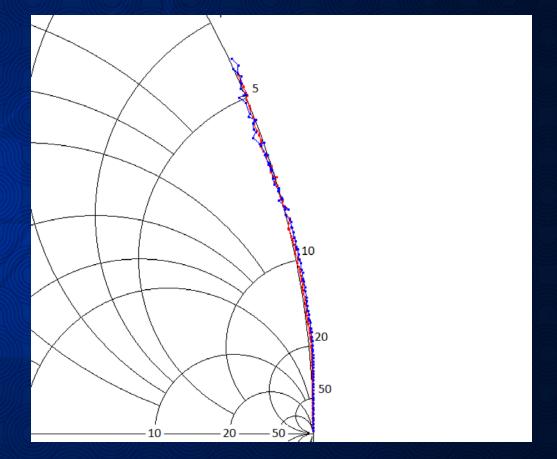

## **Improved Post-Calibration Stability**

#### **S-parameters Calibration**

#### S-parameters+Power Calibration

After Cal

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Choon Beng Sia Ph.D.

110

Frequency (GHz)

## **Improved Post-Calibration Stability**

#### **S-parameters Calibration**

#### **S-parameters+Power Calibration**

110 GHz Cal. Valid for only 10 mins110 GHz Cal. Valid for 4 hoursChoon Beng Sia Ph.D.1st Annual SWTest Asia | Taiwan, October 18-19, 2018

## Summary

- What is 5G and its Impacts.

- Identify 2 Key Challenges for 5G Wafer-Level Tests.

- Handling Large RF Channels ; Ensuring Excellent Signal Integrity

- In-membrane Antennas is feasible for 5G Production Tests.

- Reduce RF channels without expensive tester upgrades

- Good signal integrity that will support 5G production test

- More designs are now being experimented at Intel

#### Excellent Signal Integrity is Critical for Accurate 5G Tests.

- Strongly Recommend Dedicated Calibration Substrates & Post-cal. Verifications.

- Periodic System Stability Checks are Essential.

- Power Calibration improves Stability Performance & Test Throughput.

## Acknowledgements

#### Colleagues at FormFactor USA

- Dr Daniel Bock

- Amy Leong, Chief Marketing Officer

- Colleagues at Intel

- Michael Engelhardt, Michael Hemena, Robert Murphy, and Balbir Singh

## **Additional Slides**

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Choon Beng Sia Ph.D.

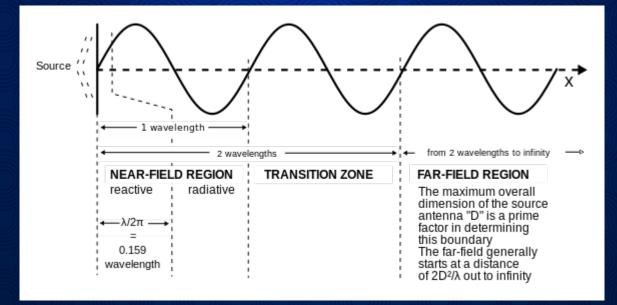

## Distance to Antenna – Near field vs. Far-field

- A Full Antenna needed?

- Typical Separation =  $100\mu m$ , at 30GHz Wavelength = 10 mm

- Less than 1 wavelength, so the field distribution will depend upon the distance from the antenna

Choon Beng Sia Ph.D. 1st Annual SWTest Asia | Taiwan, October 18-19, 2018

#### 33

## **Insertion Loss on Pad**

- Some Signal gets through on the Standard Test pad

- But the reception is not as clean across frequency

1st Annual SWTest Asia | Taiwan, October 18-19, 2018

Choon Beng Sia Ph.D.

# 38 GHz CW Spectrum showing repeatability This is Continuous Wave (CW) Spectrum measured with the ¼-antenna signal path

Choon Beng Sia Ph.D.

## Simulation of FeinProbe® Probe Card Model for a 5G WLCSP Application

| Krzysztof Dabrowiecki | Jose Moreira | Thomas Gneiting | Paul Hurst |

|-----------------------|--------------|-----------------|------------|

| Adrian Lim            |              | Ali Abdallah    |            |

| FEINMETALL            | ADVANTEST    | AdMOS           | HARBOR     |

Taiwan, October 18-19, 2018

## Overview

- Introduction

- Motivation

- 5G application test challenges

- FeinProbe<sup>®</sup> model simulation up to 30GHz

- Probe head design optimization

- Summary and Conclusion

- Follow-On Work

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

## Introduction

#### FeinProbe<sup>®</sup> Solution for WLCSP Applications

Krzysztof Dabrowiecki

June 4-7, 2017

- Diversification of semiconductor products

- WLCSP market drivers

- WLCSP electrical and mechanical requirements

- Internal qualification and various tests of spring pin as one of few technologies for WLCSP testing

http://www.swtest.org/swtw\_library/2017proc/PDF

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

## **5G - Technology and Life Evolution**

**5G Strategy for Germany**

Source: Companies and government materials Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

56

VISION

SAMSUNG ELECTRONICS

## **5G Application Test Challenges**

####

- Frequency range from 24 GHz to 44 GHz (might change!)

- Modulation frequency in the range of 800 MHz

- Devices with antennas integrated in package require over the air test at package level

- Silicon vendors would like to keep testing infrastructure modifications as small as possible

- Costs of test is critical

####

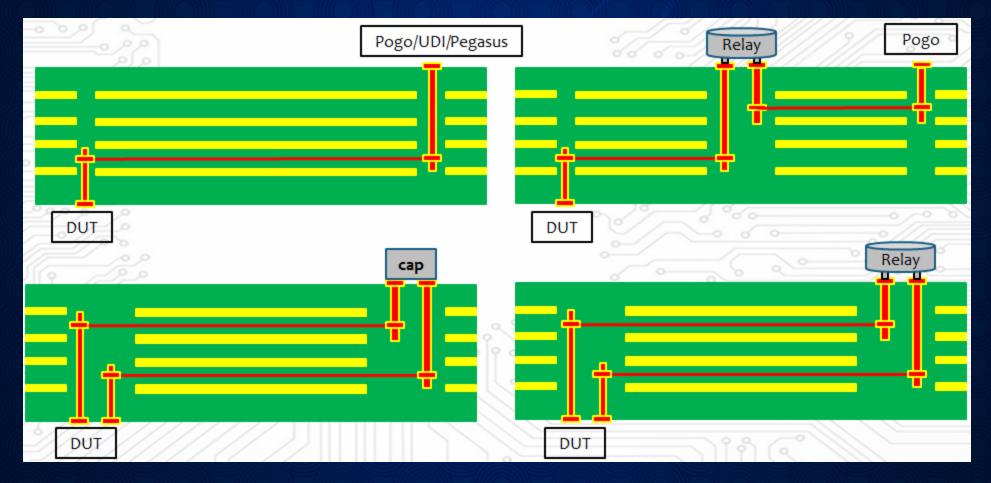

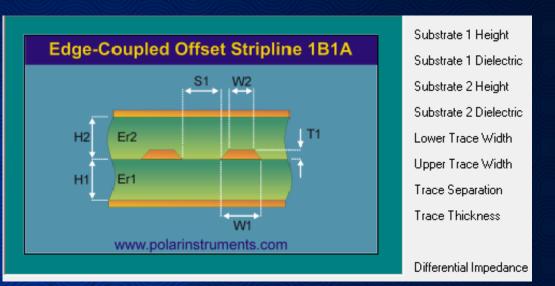

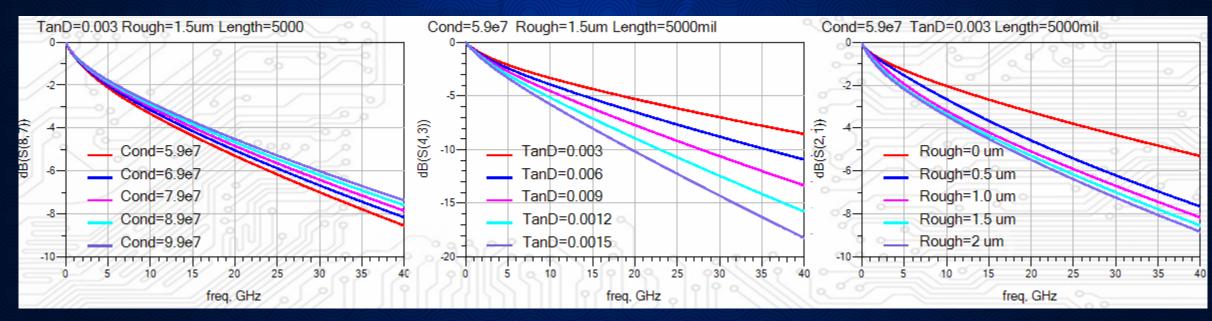

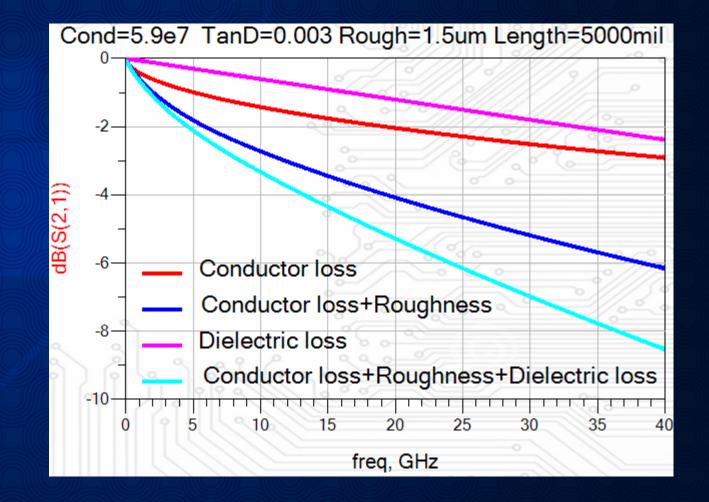

- PCB size (can be as larger than 600x500mm)

- Material choice

- Copper profile, micro-strip plating

- Signal trace type

- PCB stack-up

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

## Wafer Probing Technologies for 5G

#### Membrane Probe Technology

- Validated for mmWave frequencies and in use by several IC companies

- Good electrical performance

- High cost and long lead time

- Limited compliance

- Very limited repairability

#### MEMS Probe Technology

- Very small probe size

- Tough to get controlled impedance

- Lower inductance than cantilever

- Not yet proven for mmWave frequencies

#### **Cantilever Probe Technology**

- Uncontrolled impedance

- Very high inductance

- Bandwidth <2GHz

- Limited DUT bump and multi-DUT layouts

- Decoupling components far from DUT's

- Limited repairability

#### Spring Contact Probe Technology

- Stable and consistent contact resistance

- Self-aligning crown plunger tip

- Bandwidth >20GHz

- High Current Carrying Capability (CCC)

- Low cost and lead time

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

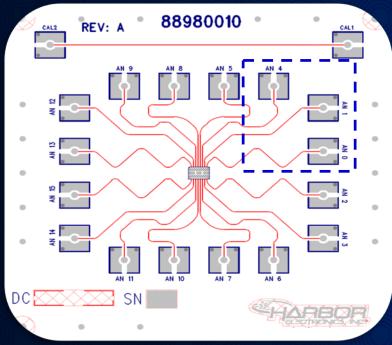

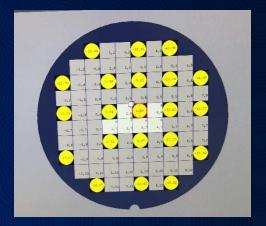

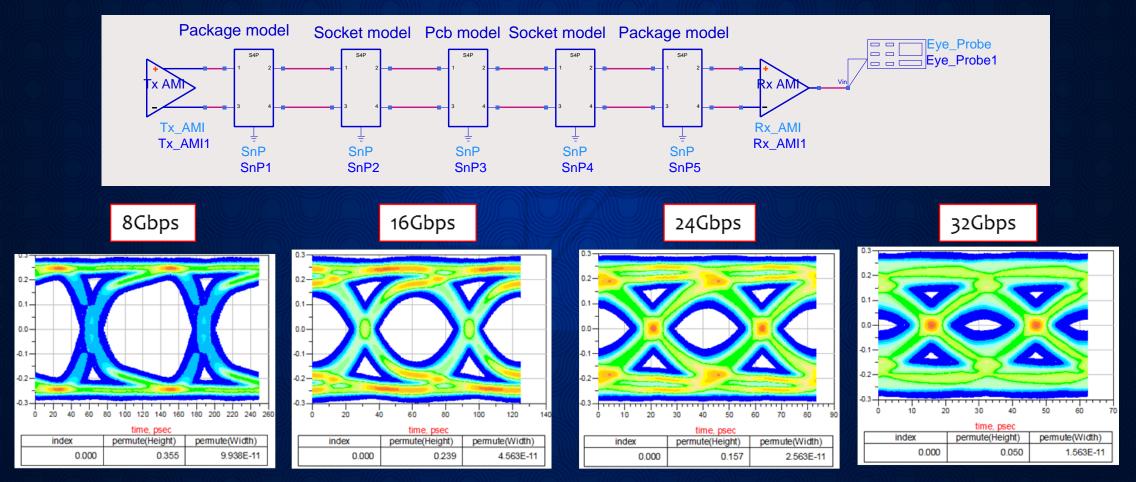

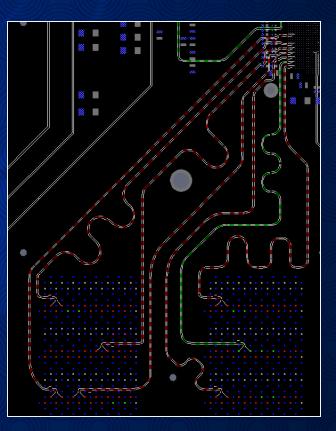

## **5G Simulation WLCSP Project**

#### Description

- The RF probe card simulation analysis includes the wafer solder bump, probe head and contact with the PCB and PCB traces up to perfect termination measurement interface

- The single die layout shows 16 RF peripheral ports

#### Scope

Dabrowiecki, Moreira,

Hurst

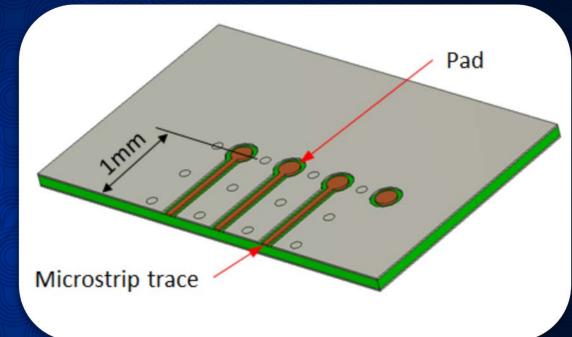

- The board is a single site WLCSP board which is for a 5G application operating at ~29 GHz.

- The transmission lines is connected from the probe head via a micro-strip trace to a suitable connector. A cable then makes the connection to a blind-mate connector

- Simulation includes BGA ball, probe head model, pad on PCB, 1.0 mm of transmission line with perfect termination

- In the probe head is used an uncompressed spring probe of 3.7mm length.

- Simulation shows the results for impedance, insertion/return loss and crosstalk

1st Annual SWTest Asia | Taiwan, October 18-19, 2018 Lim, Gneiting, Abdallah,

## **RF Simulation Project**

#### **RF pin locations**

- Device pitch ~0.4mm

- Equal trace lengths 38.8mm

#### **PCB** stack-up

| Layer<br>Number                   | Layer Type<br>Signal/ Plane | Layer Name | Cu<br>oz.               | Wt.<br>mils    | Dielectric<br>Material | Dielectric<br>Thicknes:<br>(mils) |

|-----------------------------------|-----------------------------|------------|-------------------------|----------------|------------------------|-----------------------------------|

| -                                 |                             |            |                         |                |                        |                                   |

| 1                                 | Тор                         | Тор        | 0.5 oz.                 | 0.7            | Foil                   |                                   |

|                                   |                             |            |                         | Tachyon        | Pre-Preg               | 4.2                               |

| 2                                 | Plane                       | GND        | 0.5 oz.                 |                |                        |                                   |

|                                   |                             |            | -                       | Tachyon        | Core                   | 5                                 |

| 3                                 | Plane                       | GND        | 0.5 oz.                 | 0.7            |                        |                                   |

|                                   |                             |            | PROPERTY CALLSON OF MAN | FR4            | Pre-Preg               | 6                                 |

| 4                                 | Signal                      | SIG        | 0.5 oz.                 |                |                        |                                   |

|                                   |                             |            | -                       | FR4            | Core                   | 5                                 |

| 5                                 | Plane                       | GND        | 0.5 oz.                 | 0.7            |                        |                                   |

| 12                                |                             |            | -                       | FR4            | Pre-Preg               | 90                                |

| 6                                 | Plane                       | GND        | 0.5 oz.                 | 0.7            |                        |                                   |

|                                   |                             |            | Constant and the        | FR4            | Core                   | 5                                 |

| 7                                 | Signal                      | SIG        | 0.5 oz.                 | 0.7            |                        |                                   |

| 8                                 | _                           |            |                         | FR4            | Pre-Preg               | 6                                 |

| 8                                 | Plane                       | GND        | 0.5 oz.                 | 1 100 States 1 |                        |                                   |

| 9                                 | Cinnel                      | SIG        | 0.5 oz.                 | FR4            | Core                   | 5                                 |

| 9                                 | Signal                      | 516        | 0.5 oz.                 |                | Dec Dece               | 6                                 |

| 10                                | Plane                       | GND        | 0.5 oz.                 | FR4            | Pre-Preg               | 0                                 |

| 10                                | Plane                       | GND        | 0.5 02.                 | Tachyon        | Core                   | 5                                 |

| 11                                | Plane                       | GND        | 0.5 oz.                 |                | Core                   | 0                                 |

|                                   | Fialle                      | GND        | 0.5 02.                 | Tachyon        | Pre-Preg               | 4.2                               |

| 12                                | Bottom                      | Bottom     | 0.5 oz.                 | 0.7            | Foil                   | 4.2                               |

|                                   | DOROTT                      | Dottom     | 0.5 02.                 |                | 1.011                  |                                   |

| Thicknes                          | e Paquirament               | Nominal    | Upper                   | Lower          |                        | Stack-Up                          |

| Thickness Requirement<br>(inches) |                             | .150+/010  | 0.16                    | 0.14           |                        | Estimate                          |

| (inclies)                         |                             |            |                         |                |                        | Loundto                           |

- PCB material FR4 and Isola Tachyon® 100G

- PCB thickness 149.8 mils (3.8mm)

#### **Simulated trace**

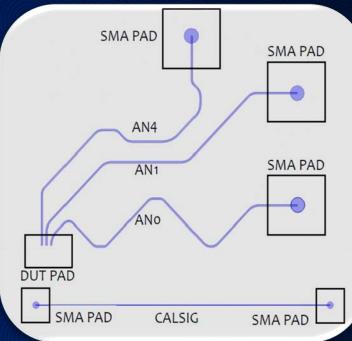

• Simulation of trace AN0, AN1 and AN4

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

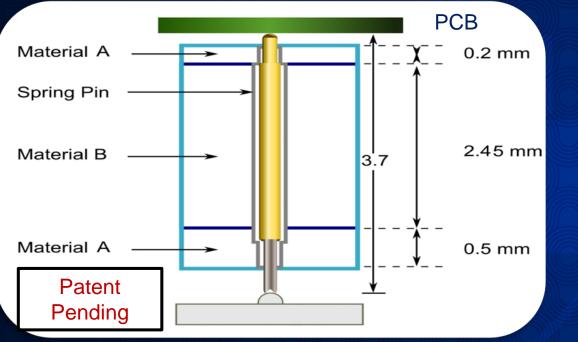

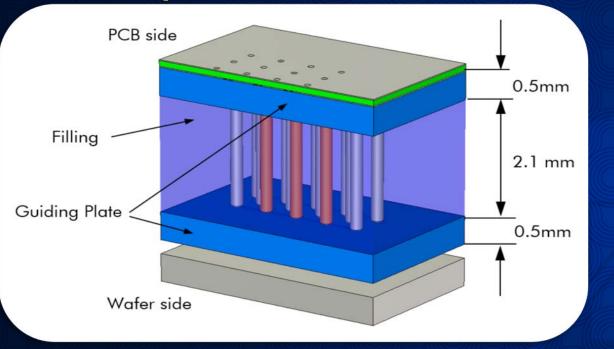

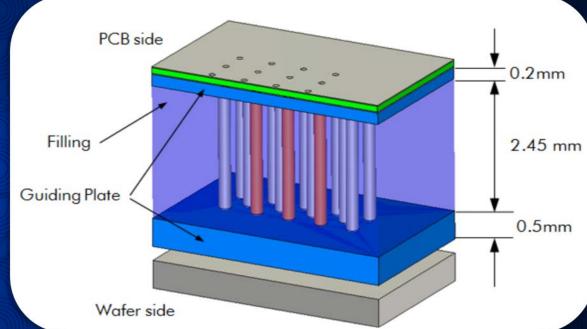

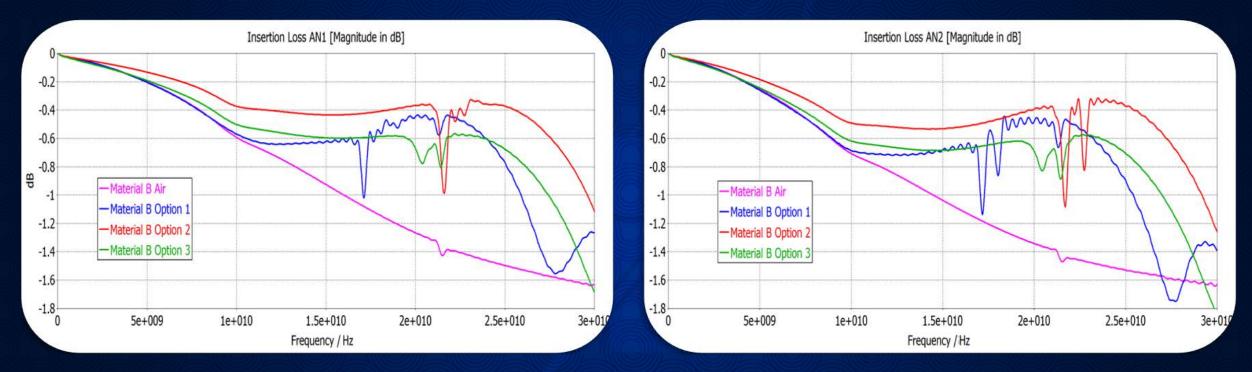

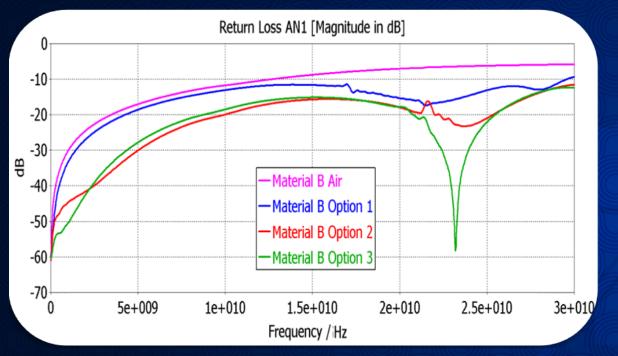

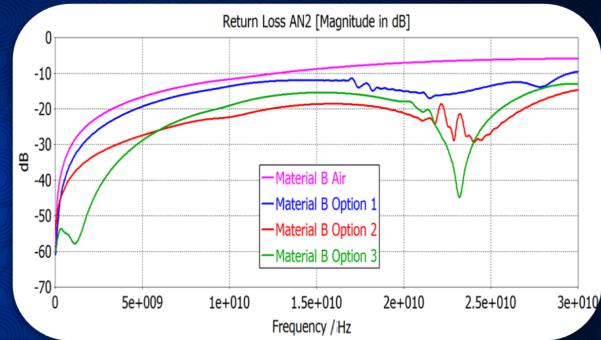

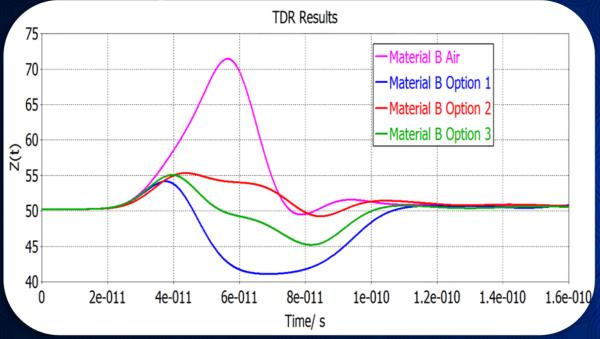

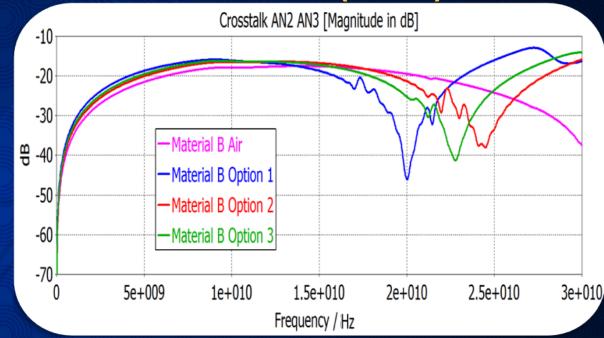

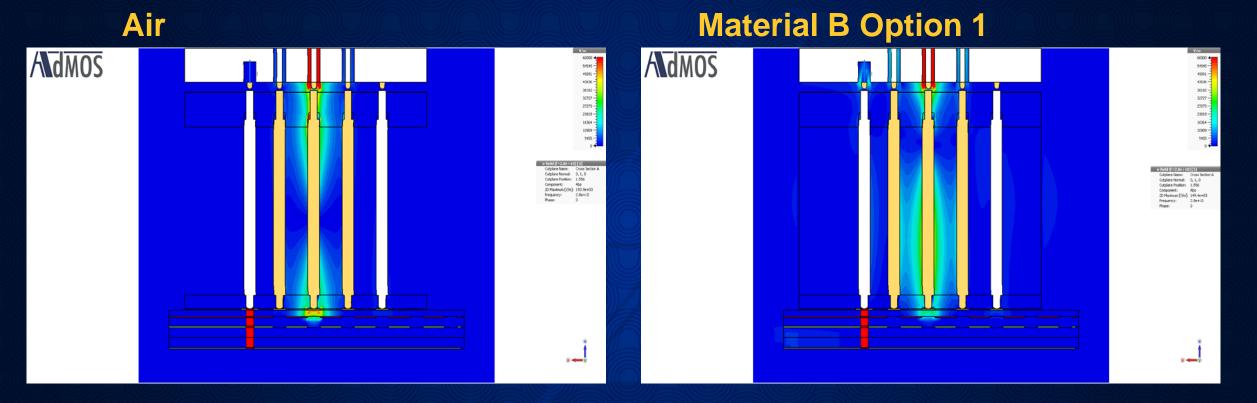

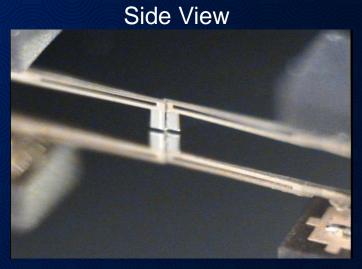

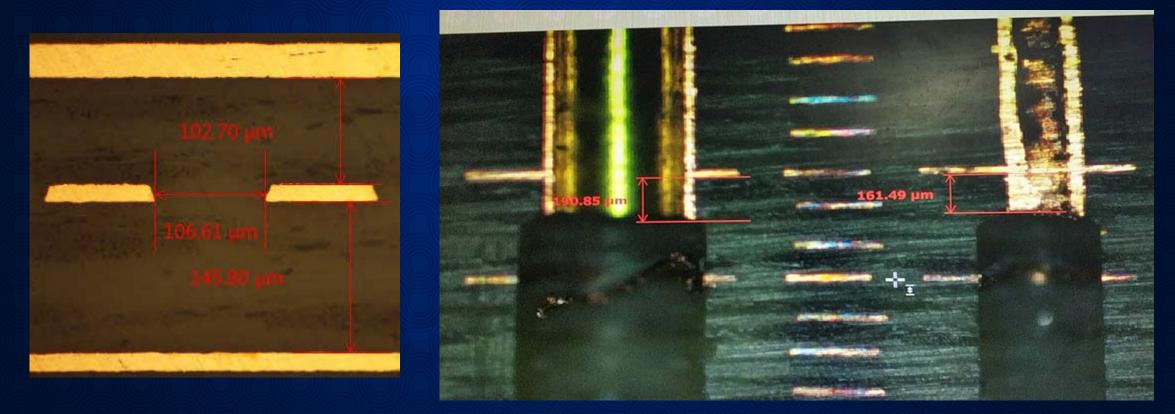

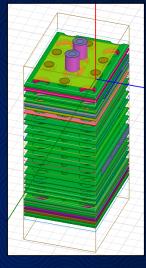

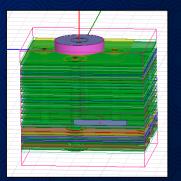

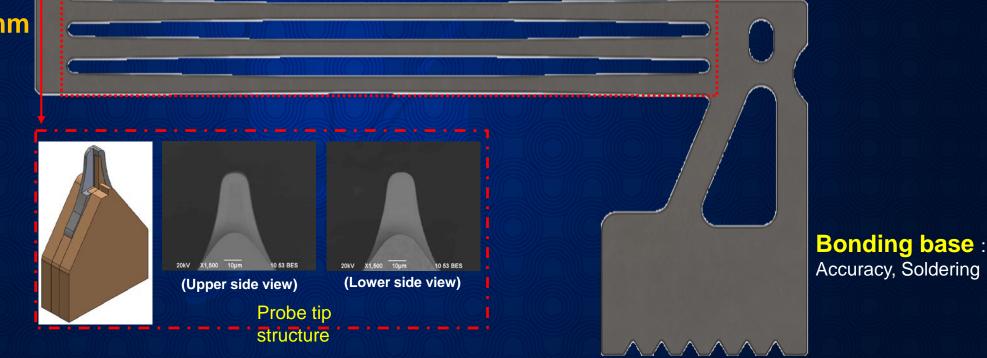

## **Spring Contact Probe Head Investigation**

#### Spring contact probe head model

- Material choice critical for signal performance

- Different materials were investigated with air between guiding plates as a reference

- Probe length 3.7 mm uncompressed

- Maximum compressed length 3.4 mm

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

#### **PCB simulation model**

The textbook micro-strip definition of a rectangular conducting cross-section between an inhomogeneous dielectric and air is far away from the reality of an ATE PCB micro-strip geometry

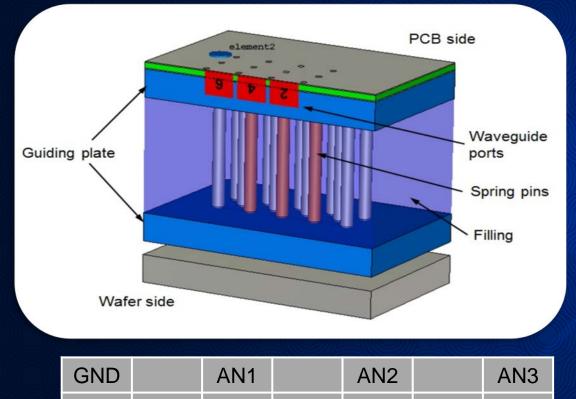

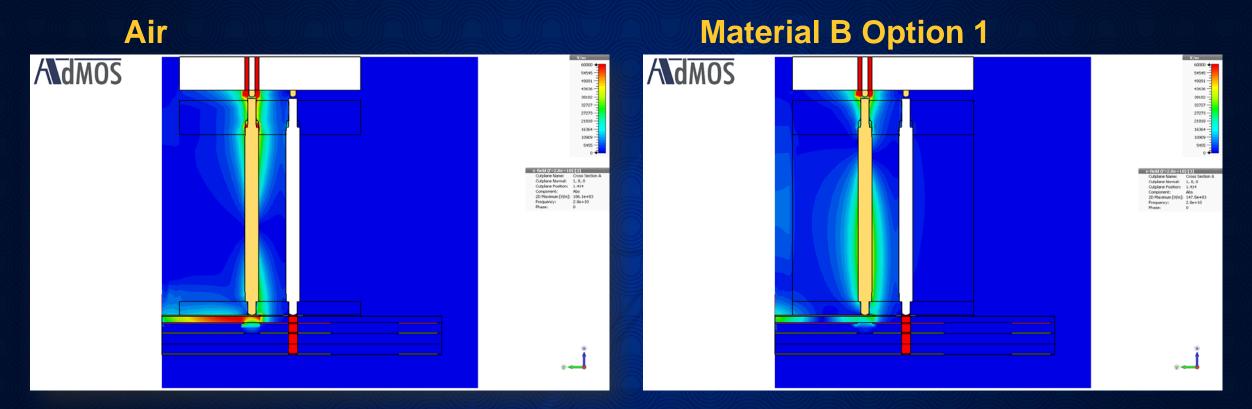

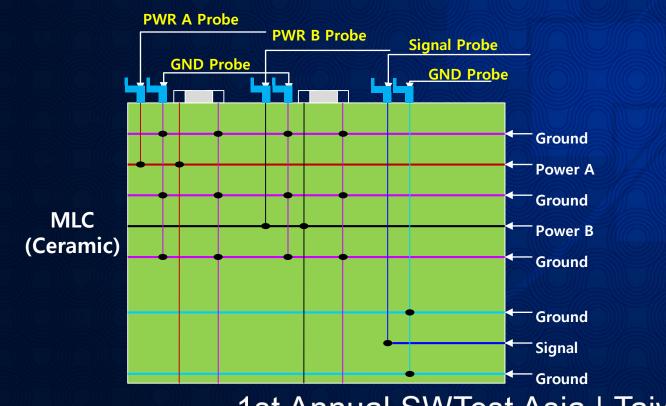

## **3D EM Simulation Model**

#### **3D probe head model**

GND

PWR

GND

**PWR**

PWR

| Component     | Material                    | Dielectric<br>constant ε <sub>r</sub> | Loss tangent tan $\delta$ | Electric cond.<br>(S/m) |

|---------------|-----------------------------|---------------------------------------|---------------------------|-------------------------|

| Guiding plate | Material A                  | XXX                                   | 0.001                     | /                       |

| Pogo Pins     | CuSn6                       | /                                     | /                         | 8e6                     |

| Ground        | CuSn6                       | /                                     | /                         | 8e6                     |

| Bump          | Sn (Tin)                    | /                                     | /                         | 8.7e6                   |

| Micro strip   | Cu                          | /                                     | /                         | 5.96e7                  |

| Isolator PCB  | Isola                       | 3.5                                   | 0.005                     | /                       |

| Filling       | Material B<br>(with option) | 1.0                                   | 0.002                     | /                       |

| РСВ           | Isola Tachyon               | 3.02                                  | 0.0021                    | /                       |

- WLCSP DUT with ~0.4 mm pitch between antennas outputs and the two adjacent GND pads

- A microstrip trace with 1.0 mm length and 0.2mm wide in Isola Tachyon dielectric was also included

- Transition to the micro-strip trace included

- AN1, AN2 and AN3 are the RF outputs

- PWR pins were shorted to GND for simulation

- 3D EM simulation performed in CST

Dabrowiecki, Moreira, Lim, Gneiting, Abdallah, Hurst

**PWR**

**GND**

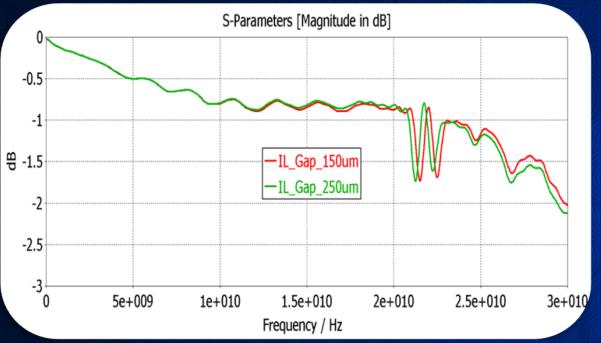

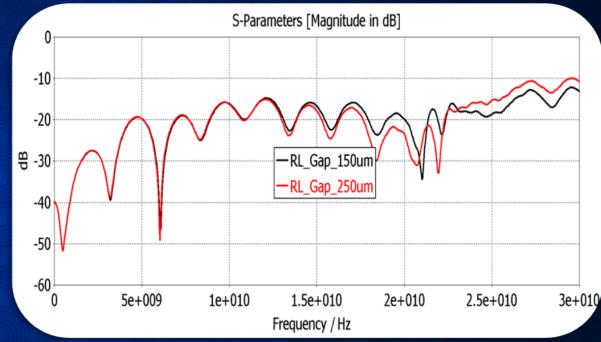

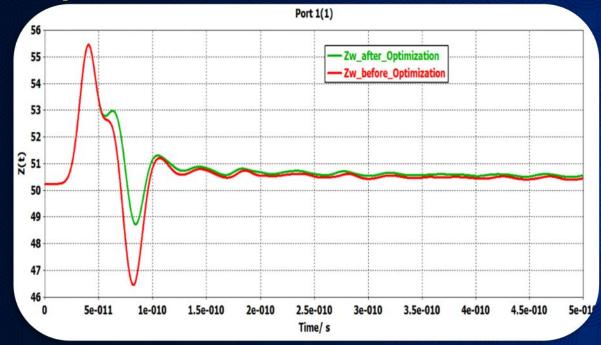

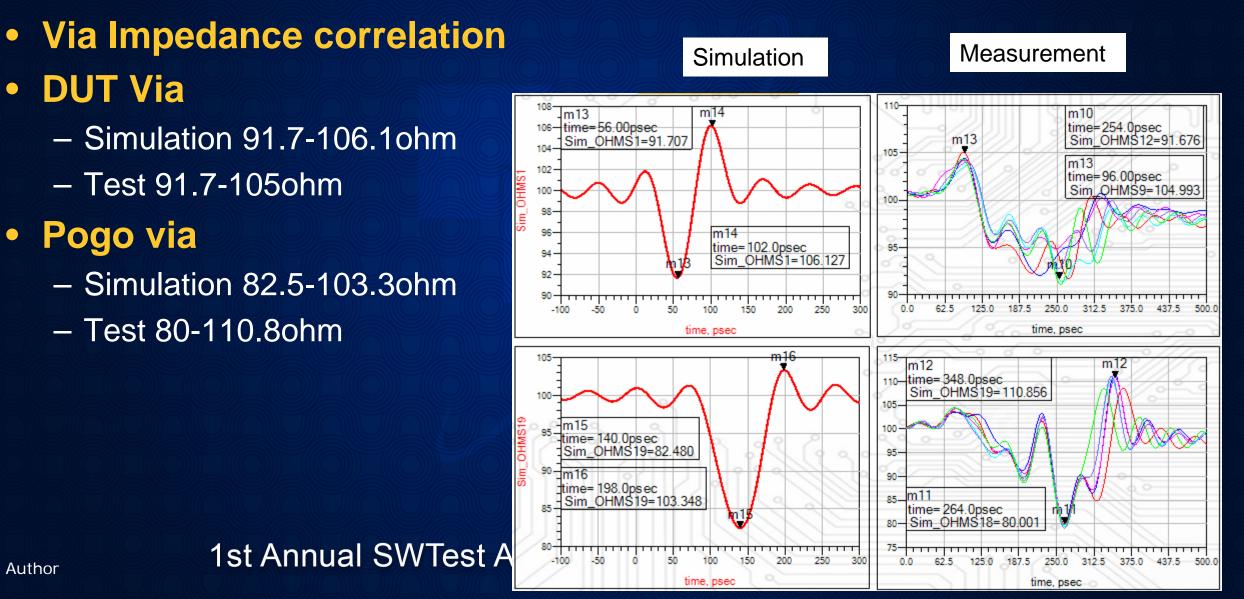

## **Probe Head Design Optimization**

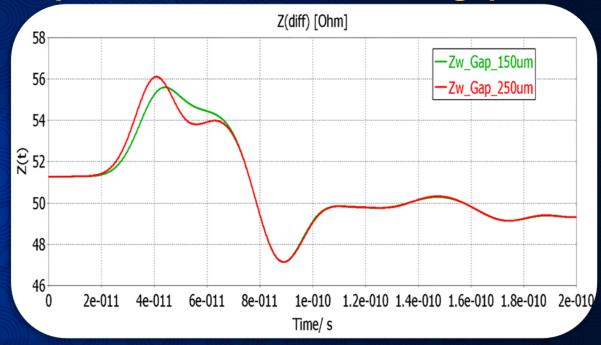

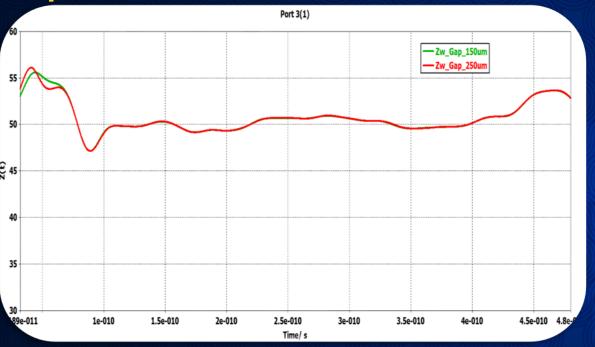

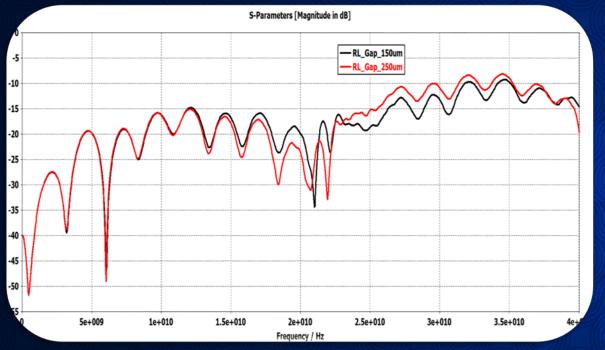

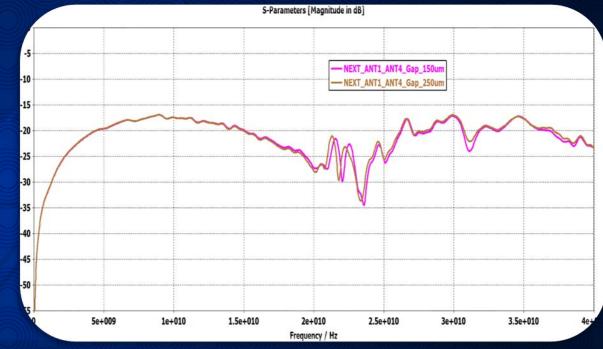

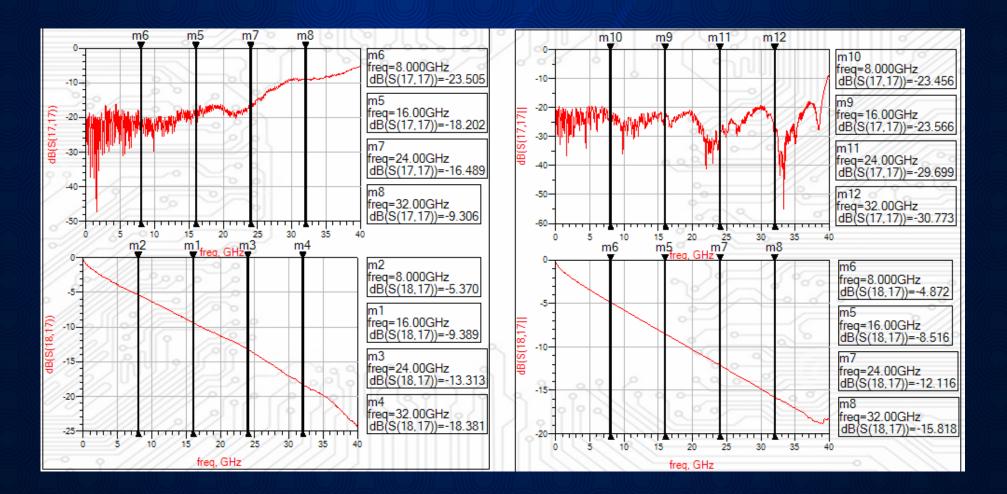

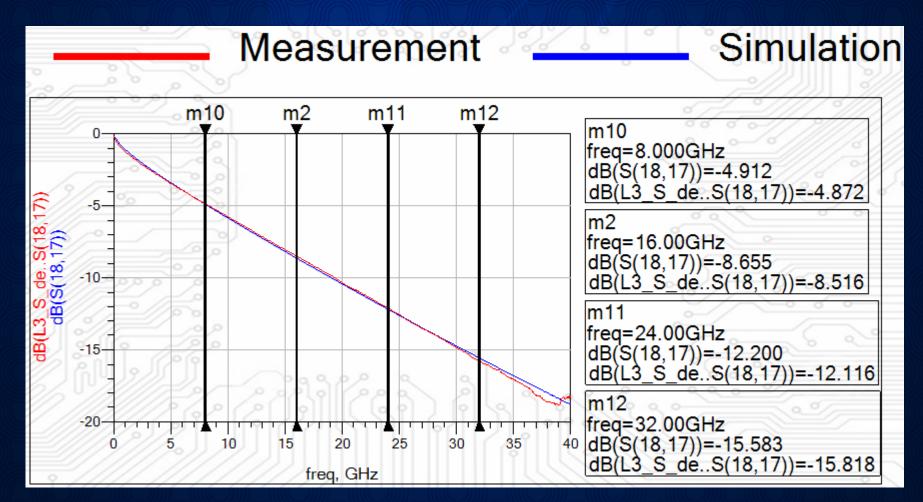

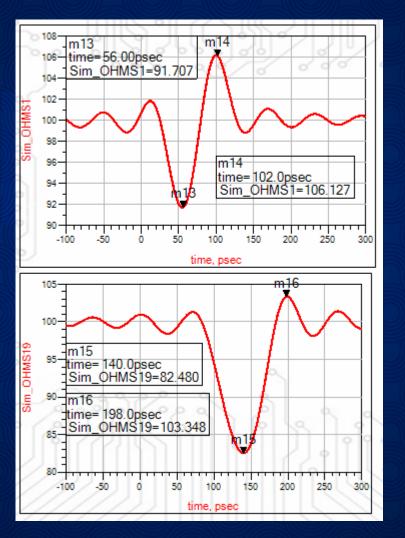

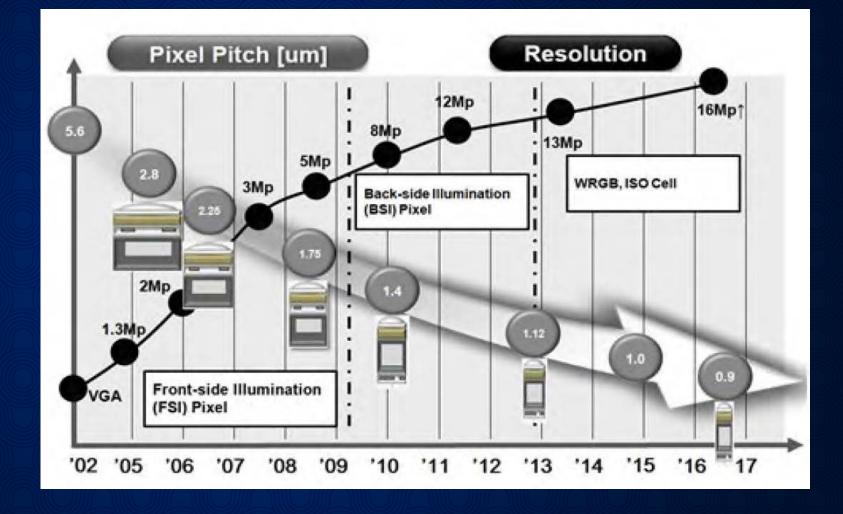

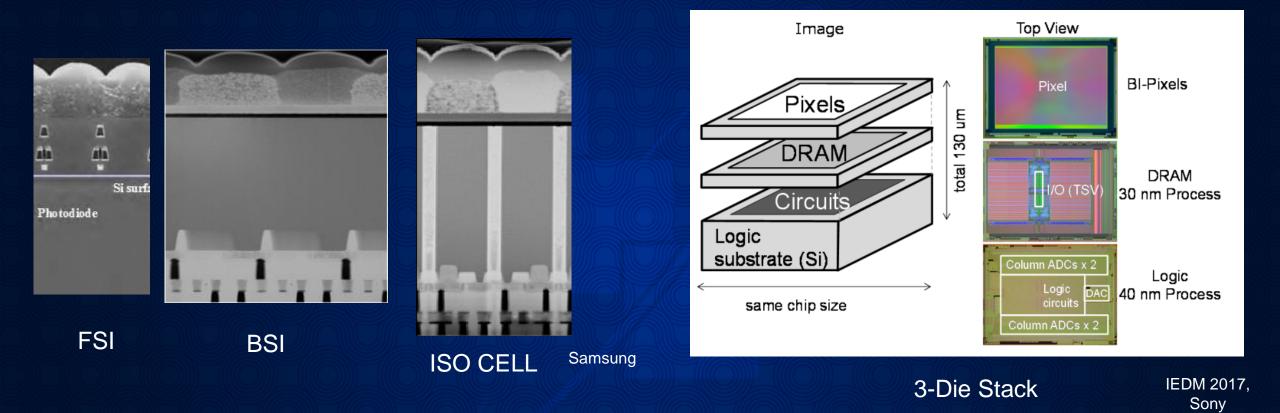

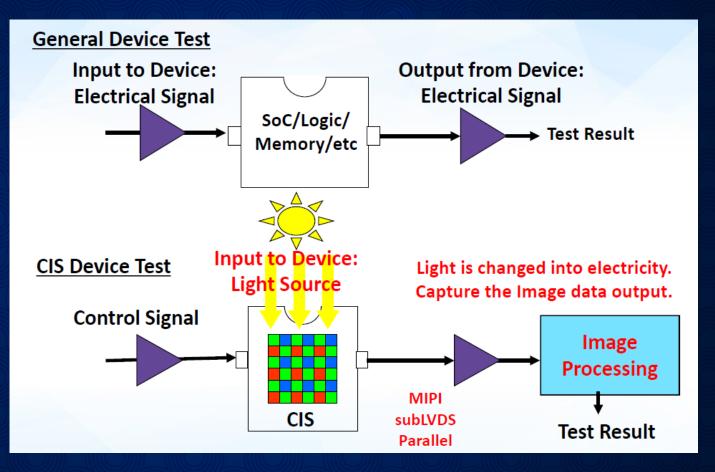

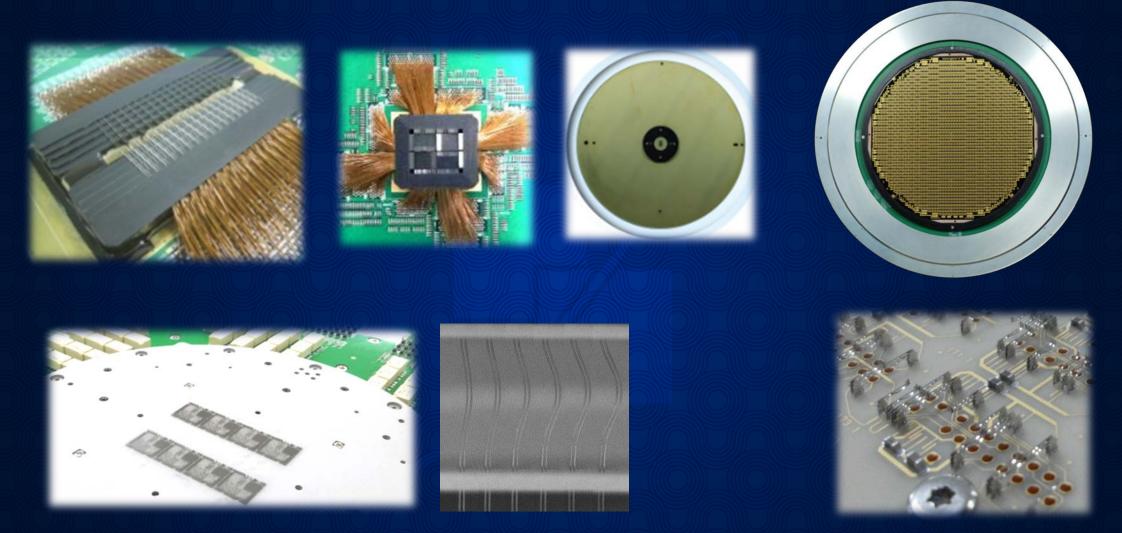

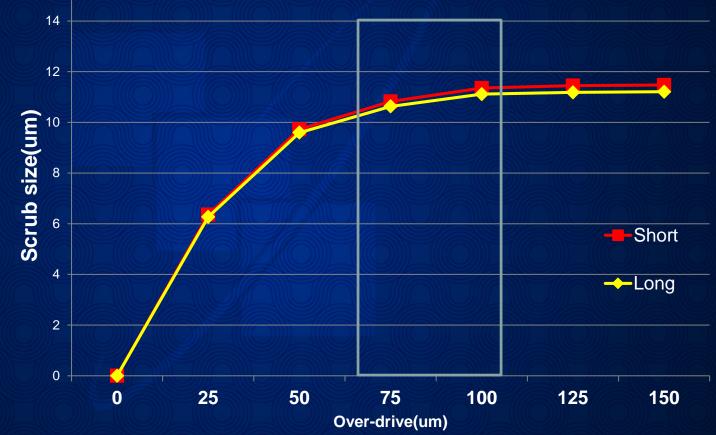

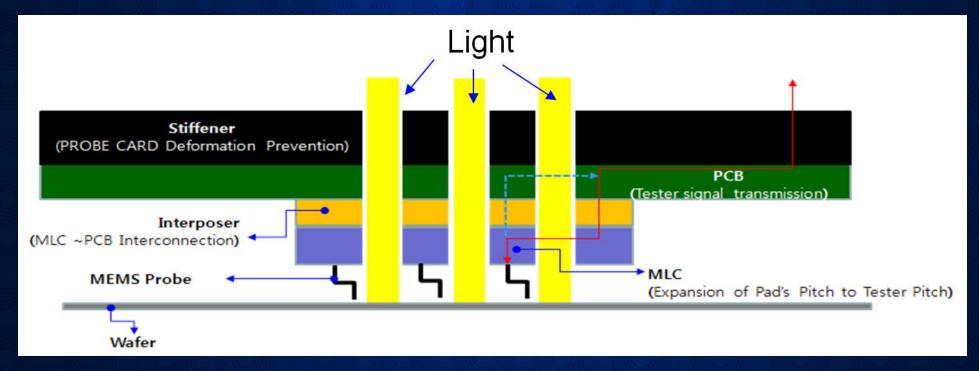

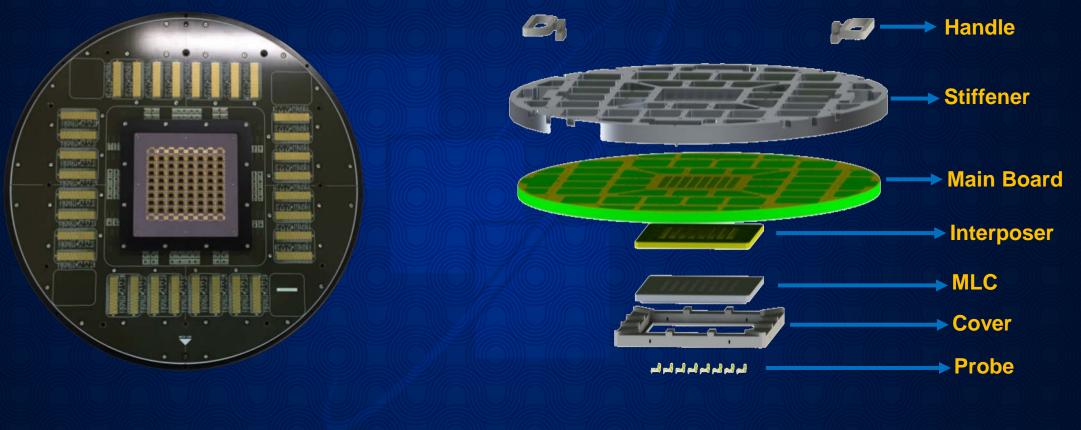

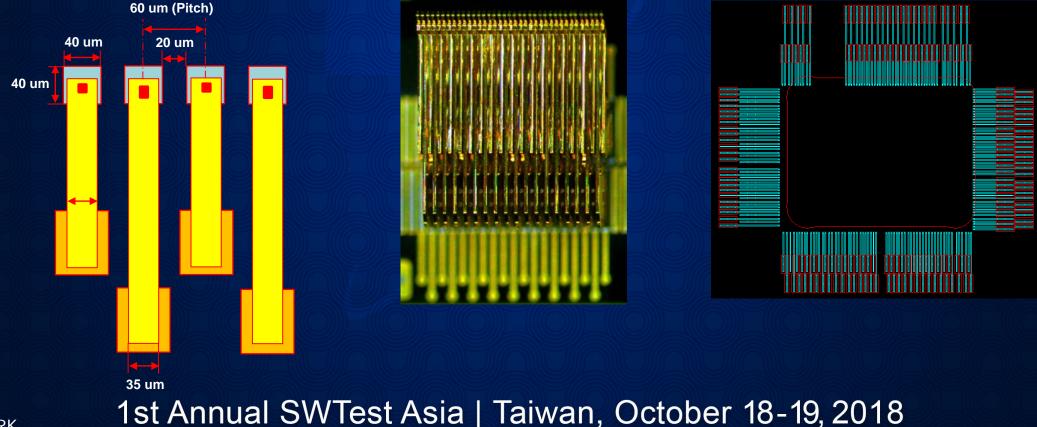

#### **Before Optimization**